# Consiglio Mazionale delle Ricezche

# ISTITUTO DI ELABORAZIONE DELLA INFORMAZIONE

PISA

COLLEGAMENTO MFA - PC IBM E COMPATIBILI

M. Chimenti, E. Fantini

Nota interna B4-12

Aprile 1987

### COLLEGAMENTO MFA - PC IBM E COMPATIBILI

#### M. Chimenti. E. Fantini

# 1) Requisiti di pilotaggio dell'MFA.

I microfotometri a controllo numerico MFA [1,2] ricevono da calcolatore i comandi necessari per la scansione di un'immagine, ed inviano in risposta dati di acquisizione e informazioni relative allo stato: le informazioni trasmesse nei due versi sono sincronizzate tramite gli impulsi di Device Command, forniti dal calcolatore e di Device Flag, emessi dall'MFA.

I comandi di funzionamento vengono inviati separatamente su quattro

linee per eseguire le operazioni di spostamento del carrello nel verso

positivo o negativo e di scansione di riga.

In base al comando ricevuto l'MFA risponde con:

- un impulso DF (Device Flag) a passo avvenuto, dopo la ricezione del comando di spostamento elementare (movimento di un passo)

- una serié di 2048 dati di acquisizione, sincronizzati da altrettanti

DF, dopo la ricezione del comando di scansione elementare (lettura di una riga).

I dati sono codificati su un byte e sono trasmessi su 8 linee; altre due linee sono richieste per la codifica dello stato: il collegamento tra l'MFA ed il calcolatore ospite richiede dunque un'interfaccia I/O di tipo parallelo a 16 bit inserita nel calcolatore. L'interfaccia deve garantire la trasmissione di dati a velocita` di almeno 100 KHz.

### 2) Interfaccia parallela sul PC.

Per collegare il calcolatore tipo IBM PC-XT al microfotometro MFA e' stata utilizzata la scheda interfaccia parallela 8255 I/O, inseribile direttamente sul bus di espansione del sistema.

Dei vari componenti montati sulla scheda vengono utilizzati un modulo 8255 e i circuiti di decodifica dell'indirizzo di scheda.

L'8255 contiene 24 porte di I/O configurabili via software per il trasferimento di dati da e verso il bus a 8 bit del calcolatore [3].

Nell'applicazione descritta il modulo viene configurato inizialmente per il modo di funzionamento 1 (Strobed Input/Output)mediante la parola di comando 10101110 (174). In questa maniera il modulo vien suddiviso dal punto di vista logico in tre porte da 8 bit ciascuna:

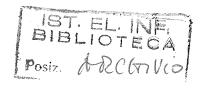

- la porta A, configurata come uscita e utilizzata per il trasferimento dei comandi verso l'MFA

- la porta B, configurata come ingresso e utilizzata per la ricezione dei dati di acquisizione

- la porta C, suddivisa in linee di ingresso e linee di uscita utilizzate per la ricezione delle informazioni sullo stato della periferica e per la sincronizzazione della trasmissione.

La fig.1 mostra lo schema logico dell'interfacciamento.

L'impulso DC, che abilità i comandi sulle linee PAO-PA3, e` ottenuto via software mediante tre scritture successive sulla porta A.

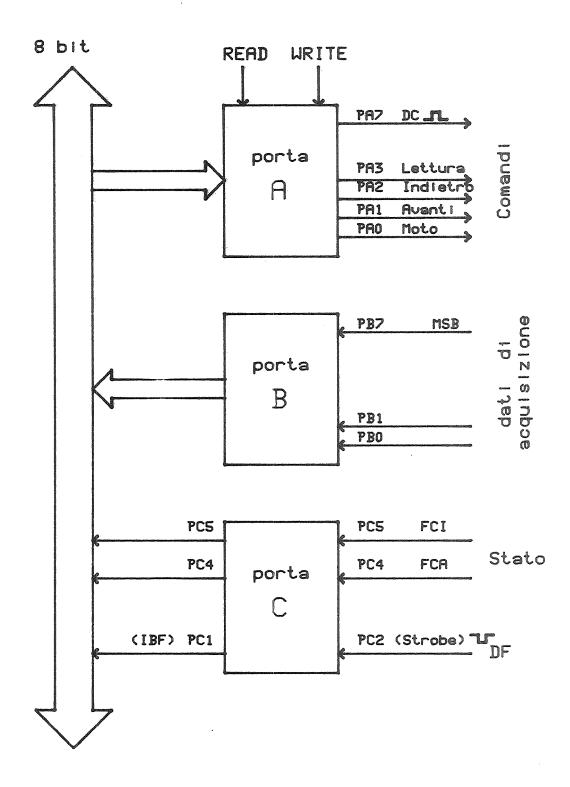

L'impulso DF, che sincronizza i dati di acquisizione inviati su PB, entra sull'ingresso PC2 = Strobe Input e mette a 1 l'uscita PC1=Input

Buffer Full; questo stato viene sentito dal programma, che provvede a leggere i dati dalla porta B, azzerando cosi' il contenuto di PC1 e predisponendosi alla ricezione dei dati successivi (vedi fig.2).

Durante le operazioni di configurazione e di comando di avanzamento del carello la scheda di interfaccia viene selezionata mediante gli indirizzi A0-A19 del bus (v. fig. 3) e la risposta ai comandi viene sentita mediante cicli di operazioni Skip on Flag su PC1; nelle operazioni di lettura di riga, l'MFA invia blocchi di dati con velocita' dipendente dal proprio orologio e superiore a 100 Kbyte ed il calcolatore deve essere pronto a riceverli: per questo scopo e' necessario effettuare la ricezione dei dati in DMA.

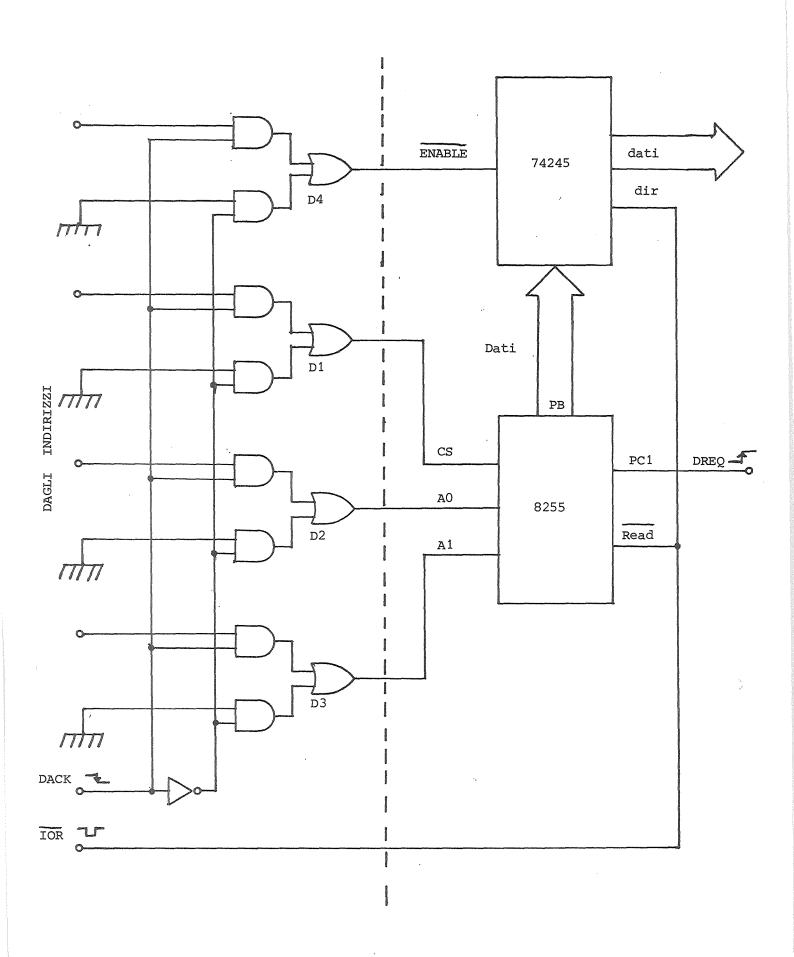

Per quanto concerne l'interfaccia di I/O, il trasferimento in DMA dalla periferica alla memoria e` gestita dalle linee DREQ (DMA Request), DACK (DMA Acknowledge) e IOR (I/O Read) del bus (v. fig.3); la scheda di interfaccia e` stata allora modificata con le variazioni mostrate in fig. 4.

In condizioni normali la linea DACK e' a 1 e quindi i deviatori  $D_{1}-D_{4}$  sono selezionati per lasciar passare i segnali dei bit di indirizzo sul bus; il modulo di I/O 8255 e l'adattatore bidirezionale 74245 vengono cosi' controllati mediante le istruzioni di ingresso e di uscita eseguite dal programma.

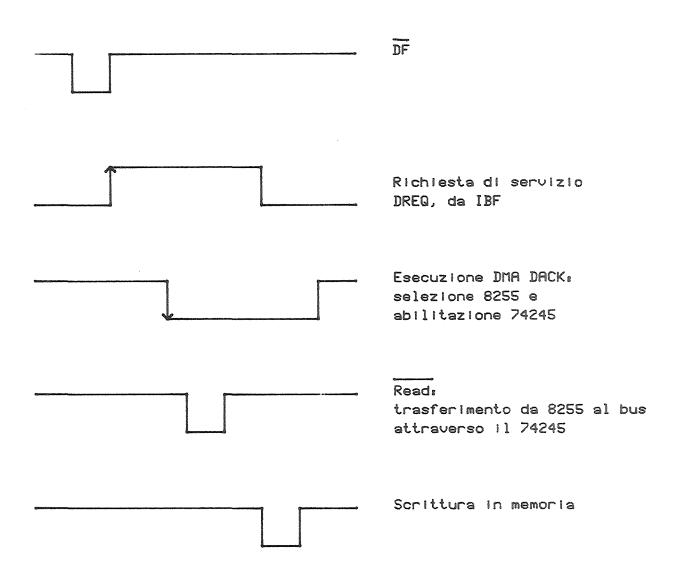

Quando il DMA del canale cui e' collegata l'interfaccia viene abilitato la transizione 0-1 di PC1, causata dall'arrivo dei dati sull'interfaccia, genera una richiesta di servizio sulla linea DREQ e il controllore del DMA risponde mettendo a zero la linea DACK. In questa condizione i deviatori  ${\rm D_1,D_2}$  e  ${\rm D_3}$  inviano sugli ingressi CS,  ${\rm A_0}$  e  ${\rm A_1}$

dell'8255 il codice 010, che abilita il trasferimento del contenuto della porta B sul bus, mentre il deviatore  $D_4$  abilita il 74245 mettendo a zero l'ingresso Enable; la lettura dei dati viene effettuata col comado IOR prodotto successivamente dal canale DMA, secondo la sequenza temporale mostrata in fig.5.

# 3) Programmazione del controllore DMA.

I trasferimenti in DMA vengono gestiti dal modulo controllore multicanale 8237 [4].

Nell'applicazione descritta il modulo viene programmato per il trasferimento di blocchi di 2048 dati (Block Transfer Mode), sul canale attivato dall'interfaccia di I/O. Il canale di trasferimento richiede dunque il caricamento dei registri:

Mode Register: Traferimento verso la memoria (Write Transfer) a blocchi (Block Mode Select).

Current Word Register: Numero di trasferimenti (= lunghezza del blocco - 1) = 2047.

Il canale di trasferimento viene abilitato solo dopo l'invio all'MFA di un comando di lettura di dati; l'avvenuta esecuzione del trasferimento viene controllata mediante la lettura del bit di canale nello Status Register, che effettua una transizione 0-1 al termine del trasferimento di un blocco di dati.

### Descrizione Driver per controllo MFA da PC

Il blocco di programmi per il controllo del microfotometro MFA consiste in due routines scritte in macro assembler Microsoft richiamabili da programmi scritti in linguaggi evoluti tipo Fortran etc.

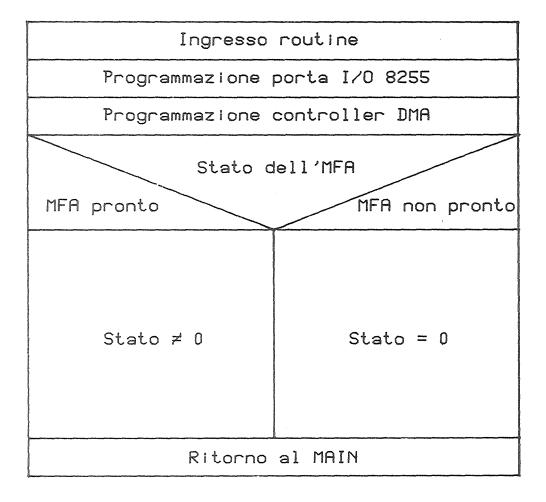

La prima routine, denominata "INIZIO", e' quella che serve per programmare sia l'interfaccia di I/O 8255 sia il controllore di DMA ad effettuare le operazioni volute dal driver vero e proprio. Tramite questa routine all'8255 viene chiesto di operare su 16 linee divise in porte di input e porte di output tramite delle scritture di determinati comandi nei registri di controllo dell'8255.

Inoltre provvede anche a programmare il controllore di DMA abilitando un singolo canale al trasferimento di blocchi di dati di 2048 bytes ogni qualvolta gli verra' richiesto tramite il settaggio di una linea di richiesta da parte della periferica.

All'uscita di questa routine si avra` un codice di stato che sara` uguale a zero se la periferica e` pronta all'uso, mentre sara` maggiore di zero se verranno riscontrate alte sia la linea di fine corsa avanti sia quella di fine corsa indietro (tipicamente quando l'MFA e` staccato dall'alimentazione di rete).

Una tipica chiamata Fortran per questa routine e`CALL INIZIO(STATO) dove STATO e` una variabile, dichiarata nel programma chiamante, di tipo INTEGER\*4.

Il driver vero e proprio cioe` la routine che e` in grado di inviare comandi all'MFA e di interpretare correttamente le varie risposte (stati) che questo invia verso il PC si chiama "LS250".

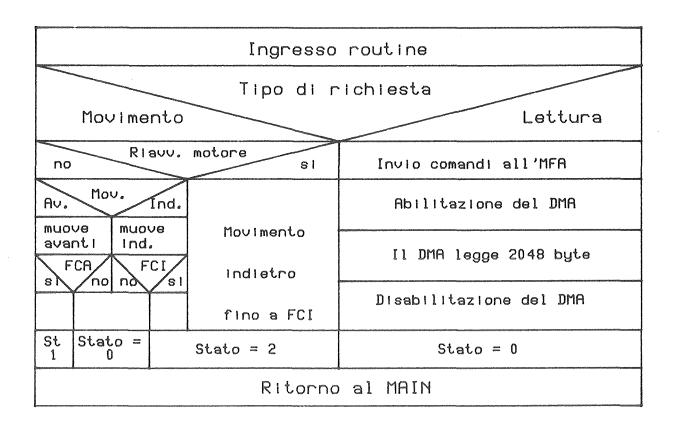

Anche questa routine come l'altra e' scritta in macro assembler Microsoft ed e' richiamabile da programmi scritti in linguaggi ad alto livello tipo Fortran, etc. La routine e' divisa logicamente in tre blocchi, il primo e' costituito dall'interprete che e' in grado di verificare se la richiesta di operazione del programma chiamante e' corretta o meno.

Le richieste possibili sono quelle di spostamento del carrello porta immagine oppure di lettura di una riga. Se l'operazione richiesta non rientra in questi due casi viene posto un parametro di ritorno al valore -1. Una volta che l'operazione richiesta e' stata riconosciuta valida il controllo passa alla parte di codice che e' in grado di soddisfarla, infatti gli altri due blocchi sono composti da istruzioni in grado di spostare il carrello avanti o indietro di n passi e controllare che cio' sia avvenuto e da istruzioni in grado di leggere una riga di immagine.

Il movimento del carrello avviene senza richieste di DMA ed inoltre viene controllato anche il verificarsi di uno stato di fine corsa, se questo avviene la routine pone il parametro al valore 1 se si richiedeva uno spostamento avanti ed e' stato trovato un fine corsa avanti mentre viene posto al valore 2 se la richiesta era di spostamento indietro e si e' verificato un fine corsa indietro.

Il parametro assumera` il valore 0 se la richiesta di spostamento ha avuto buon fine.

La richiesta di lettura riga viene interpretata e soddisfatta da un blocco di istruzioni che inviano il comando all'MFA, attivano il DMA e controllano che effettivamente vengano letti 2048 bytes. A lettura

avvenuta viene posto il parametro di ritorno al valore 0 e il controllo passa di nuovo al programma chiamante.

Una tipica chiamata Fortran e' CALL LS250(IOP, IV, IST) dove:

- IOP e' una variabile dichiarata INTEGER\*4 che puo' valere:

- IOP=1 per lettura riga

- IOP=2 per movimento carrello

- IV e` una variabile INTEGER\*2 o un vettore INTEGER\*2 dipendentemente dal valore di IOP

- se IOP=1 IV deve essere un vettore con dimensioni INTEGER\*2 di almeno 2048 elementi dove verranno inseriti i dati letti dall'MFA

- se IOP=2 IV deve essere una variabile INTEGER\*2 contenente il numero dei passi di cui si vuole muovere il carrello. Per spostamenti avanti IV>0, per spostamenti indietro IV<0</p>

- se IOP=2 e IV=0 verra` effettuato un movimento del carrello indietro fino a quando non viene incontrato un fine corsa (riavvolgimento del carrello).

- IST e' una variabile dichiarata INTEGER\*4 ed e' il parametro di ritorno con lo stato della periferica e puo' valere:

IST=1 se e' stato incontrato un fine corsa nel movimento in avanti

IST=2 se e' stato incontrato un fine corsa nel movimento indietro

IST=0 se l'operazione richiesta e' stata eseguita correttamente.

Fig. 1 - Schema logico di interfacciamento.

Fig. 2 - Diagramma temporale dell' operazione di lettura dei dati di acquisizione.

| Pin No. | Name       | Pin No. | Name           |

|---------|------------|---------|----------------|

| Al      | I/O CHECK/ | B1      | GND            |

| A2      | D7         | B2      | RESET DRV      |

| A3      | D6         | B3      | +5V            |

| A4      | D5         | B4      | IRQ2           |

| . A5    | D4         | B5      | -5VDC          |

| A6      | D3         | B6      | ·· DRQ2        |

| A7      | D2         | B7      | -12V           |

| AB      | D1         | Ba      | CARD SELECTED/ |

| A9      | D0         | B9      | -1-12V         |

| A10     | I/O CH RDY | B10     | GND            |

| All     | AEN        | B11     | MEMW/          |

| A12     | Á19        | B12     | MEMR/          |

| A13     | A18        | B13     | 10W/           |

| A14     | A17        | B14     | ior/           |

| A15     | A16        | B15     | DACK3/         |

| A16     | A15        | B16     | DRQ3           |

| A17     | A14        | B17     | DACK1/         |

| A18     | A13        | B18     | DRQ1           |

| A19     | . A12      | B19     | DACKO/         |

| A20     | A11        | B20     | CLOCK          |

| A21     | A10        | B21     | IRQ7           |

| A22 '   | Λ9         | B22     | IRQ6           |

| A23     | A8         | B23     | IRQ5           |

| A24     | A7         | B24     | IRQ4           |

| A25     | , A6       | B25     | IRQ3           |

| A26     | A5         | B26     | DACK2/         |

| A27     | Λ4         | B27     | T/C            |

| A28     | A3         | B28     | ALE            |

| A29     | A2         | B29     | +5V            |

| A30     | A1         | B30     | osc            |

| A31     | A0         | B31     | GND            |

Fig. 3 - PC bus

Fig. 4 - Schema logico delle modifiche per il funzionamento in DMA.

Fig. 5 - Diagramma temporale dell'operazione di lettura dati in DMA.

Fig. 6 - Flusso della routine di inizializzazione della porta parallela e del controllore del DMA con test sullo stato dell'MFA.

Fig. 7 - Flusso della routine per l'interpretazione ed esecuzione delle richieste all'MFA.

## RIFERIMENTI

- 1) L.Azzarelli, M.Chimenti: "Descrizione del microfotometro MFA/250/LS<sup>R</sup>", 83-P2-TERRI-4-IEPI-003

- 2) L.Azzarelli, S.Cesaro, M.Chimenti: "Caratteristiche sperimentali del dispositivo MFA/DIGIRAD<sup>R</sup>", Nota interna IEI-B4-56-1986

- 3) 8255-A Programmable Peripheral Interface Manuale INTEL pag. 6-166, 6-185

- 4) 8237 Programmable DMA Controller Manuale INTEL pag. 2-88, 2-102