# D<sub>4.3</sub> – Validation Report

| Deliverable ID      | D4.3              |

|---------------------|-------------------|

| Deliverable Title   | Validation Report |

| Work Package        | WP4               |

|                     |                   |

| Dissemination Level | PUBLIC            |

|                     |                   |

|                     |                   |

| Version             | 1.3               |

| Date                | 30/08/2019        |

| Status              | Final             |

|                     |                   |

|                     |                   |

| Lead Editor         | SIRTI             |

| Main Contributors   | CNR               |

**Published by the ASTRAIL Consortium**

# **Document History**

| Version | Date       | Author(s)                                                   | Description                                                                                 |

|---------|------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| 0.0     | 2019-05-24 | SIRTI                                                       | First Draft with TOC                                                                        |

| 0.1     | 2019-06-07 | CNR                                                         | Changes in structure and tasks distribution                                                 |

| 0.2     | 2019-06-26 | CNR                                                         | Section 3 "Moving Block and ATO Modelling" added                                            |

| 0.3     | 2019-06-27 | 6-27 CNR Section 3 "Moving Block and ATO Modelling" updated |                                                                                             |

| 0.4     | 2019-07-02 | CNR, SIRTI                                                  | Section 5 "Quantitative Verification" updated                                               |

| 0.5     | 2019-07-10 | O19-07-10 CNR Section 2 "Validation of the Process" updated |                                                                                             |

| 0.6     | 2019-07-24 | CNR                                                         | Section 4 "Qualitative verification" updated                                                |

| 0.7     | 2019-08-06 | CNR                                                         | Section 4 "Qualitative verification" updated                                                |

| 8.0     | 2019-08-09 | SIRTI                                                       | Annex A added                                                                               |

| 0.9     | 2019-08-14 | CNR                                                         | Section 4 "Qualitative verification" updated                                                |

| 1.0     | 2019-08-22 | CNR                                                         | Section 5 "Qualitative Verification" removed, "Introduction" added, Section 2, 3, 4 Updated |

| 1.1     | 2019-08-26 | CNR                                                         | Added Conclusion section                                                                    |

| 1.2     | 2019-08-27 | SIRTI                                                       | Updated Conclusion section, typo review                                                     |

| 1.3     | 2019-08-30 | SIRTI, CNR                                                  | Annex A updated. Final release.                                                             |

# Legal Notice

The information in this document is subject to change without notice.

The Members of the ASTRail Consortium make no warranty of any kind with regard to this document, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. The Members of the ASTRail Consortium shall not be held liable for errors contained herein or direct, indirect, special, incidental or consequential damages in connection with the furnishing, performance, or use of this material.

The Shift2Rail JU cannot be held liable for any damage caused by the Members of the ASTRail Consortium or to third parties as a consequence of implementing this Grant Agreement No 777561, including for gross negligence.

The Shift2Rail JU cannot be held liable for any damage caused by any of the beneficiaries or third parties involved in this action, as a consequence of implementing this Grant Agreement No 777561.

The information included in this report reflects only the authors' view and the Shift2Rail JU is not responsible for any use that may be made of such information.

# **Table of Contents**

| Do  | cumen    | t History                                                           | 2  |

|-----|----------|---------------------------------------------------------------------|----|

| Leg | gal Not  | iice                                                                | 2  |

| Tal | ble of ( | Contents                                                            | 3  |

| 1   | Intro    | oduction                                                            | 5  |

|     | 1.1      | Purpose and Scope                                                   | 5  |

|     | 1.2      | Executive Summary                                                   | 5  |

|     | 1.3      | Related documents                                                   | 7  |

| 2   | Valic    | dation of the Process                                               | 8  |

|     | 2.1      | Formal methods selection                                            | 8  |

|     | 2.1.1    | Main Output from Previous Deliverables                              | 8  |

|     | 2.1.2    | Choice of Formal Methods based on the Development Context           | 8  |

|     | 2.2      | Formal Methods Application Process                                  | 9  |

|     | 2.2.1    | Requirements Elicitation and Simulation                             | 10 |

|     | 2.2.2    | Mapping to Formal Languages                                         | 11 |

|     | 2.2.3    | Formal Verification                                                 | 11 |

| 3   | Mov      | ing Block and ATO modelling                                         | 12 |

|     | 3.1      | Simulink and Stateflow Languages                                    | 12 |

|     | 3.2      | Moving Block                                                        | 14 |

|     | 3.2.1    | -                                                                   |    |

|     | 3.2.2    | Moving-block Model Architecture                                     | 15 |

|     | 3.2.3    |                                                                     |    |

|     | 3.2.4    |                                                                     |    |

|     | 3.2.5    |                                                                     |    |

|     | 3.2.6    |                                                                     |    |

|     | 3.3      | ATO                                                                 |    |

|     | 3.3.1    |                                                                     |    |

|     | 3.3.2    |                                                                     |    |

|     | 3.3.3    |                                                                     |    |

|     | 3.3.4    |                                                                     |    |

|     | 3.4      | Integrated Model                                                    |    |

|     | 3.4.1    |                                                                     |    |

|     | 3.4.2    |                                                                     |    |

|     | 3.5      | Requirements Elicitation and Simulation with Simulink: Observations |    |

| 4   |          | litative verification                                               |    |

|     | 4.1      | The UML system description                                          |    |

|     | 4.1.1    |                                                                     |    |

|     | 4.1.2    |                                                                     |    |

|     | 4.1.3    | -                                                                   |    |

|     | 4.1.4    | 5                                                                   |    |

|     | 4.1.5    |                                                                     |    |

|     |          |                                                                     |    |

|      | 4.1.6     | ATO                                          | 44 |

|------|-----------|----------------------------------------------|----|

| 4    | .2 T      | he EventB/ProB modelling                     | 46 |

| 4    | .3 T      | he EventB/ProB verification                  | 50 |

|      | 4.3.1     | Moving Block verification                    | 51 |

|      | 4.3.2     | ATO verification                             | 55 |

|      | 4.3.3     | Integrated Moving Block and ATO verification | 57 |

| 4    | .4 C      | bservations                                  |    |

|      | 4.4.1     | Correctness of the system design             | 59 |

|      | 4.4.2     | Correctness of the ProB translation          |    |

|      | 4.4.3     | Correctness of the LTL formulas              | 60 |

|      | 4.4.4     | Correctness of the ProB tool                 | 60 |

|      | 4.4.5     | Current limits of our approach               | 60 |

| 5    | Conclu    | ısions                                       | 62 |

| Acro | onyms     |                                              | 64 |

| List | of figur  | es                                           | 65 |

| Anr  | iex A – 9 | System Requirements                          | 66 |

|      |           |                                              |    |

# L Introduction

### 1.1 Purpose and Scope

Formal methods are mathematically-based techniques to support the development of software intensive systems [23][22]. Normally, formal methods oriented to design and verification of systems include (i) a **modelling language**, which is used to model a system, and (ii) a **verification strategy**, which is used to verify properties on the system. Formal methods are usually associated to formal tools, which can provide textual or visual editors to create a model of the system, as well as automated verification capabilities. Formal methods have been largely applied in industrial projects, especially in the safety-critical market, including railways [24]. However, it cannot yet be said that a single mature technology has emerged.

The Work Package 4 (WP4) of the ASTRail project aims to identify, based on an analysis of the state-of-theart and on concrete trials, the candidate set of formal and semi-formal methods that appear as the most adequate to be used in the railway context. In the following, when we will use the general term "formal method", we will implicitly include also semi-formal methods, i.e. those methods that use languages for which the semantics is not formally defined but depends on their execution engine.

Since formal methods are normally associated with tools, we will also use the terms formal methods and formal tools interchangeably.

To address the goal of identifying the most adequate formal methods, WP4 is structured into four tasks (T4.4, in bold, is the focus on the current deliverable):

- Task 4.1 Benchmarking: this task aims at studying the state-of-the-art and state of the practice of formal and semi-formal methods, by gathering knowledge from the literature and railway practitioners.

- Task 4.2 Ranking: this task aims at providing a ranking matrix to support the selection of the most adequate formal methods to be used in a certain development context.

- Task 4.3 Trial Application: this task aims at experimenting the usage of a set of selected formal methods through the modelling of the moving-block system, from Task 2.1.

- Task 4.4 Validation: this task aims at validating the usage of the selected formal methods by integrating the moving-block model with the automated driving technologies from Task 3.3.

The current deliverable D4.3 Validation Report is the output of Task 4.4 – Validation. The results of Task 4.1-2 and 4.3 have been reported in D4.1 [RD.1] and D4.2 [RD.5] respectively.

### 1.2 Executive Summary

The description of Task 4.4 - Validation Report is as follows:

In order to validate the choices and techniques consolidated in task T4.3 we will address, in collaboration with the other partners of the project, the modelling of the integration of Moving Block with Automated Driving Technologies (from T.3.3), providing for each considered item a full model that will represent a rigorous and verifiable definition of functional, interoperability and dependability requirements.

In Task 4.3 a series of formal techniques were evaluated and a main output of the task was that a combination of techniques is required to address different needs and phases of the railway process. Combinations of techniques should be chosen based on the context. Therefore, validating choices and techniques, as discussed in the proposal, implies defining and assessing a formal development process that is appropriate for the current context of development. Hence, this deliverable is concerned with the validation of a proposed formal process, by means of modelling and verification, applied to Moving Block with Automated Driving Technologies.

In the context of the ASTRail project, both Moving Block and Automated Driving Technologies (referred in the following as Automated Train Operation or ATO) can be considered as being at the *concept* phase of development. Indeed, preliminary requirements were defined for the Moving Block (see [RD.5]), and only high-level functions were defined for the ATO in Task 3.3 (see [RD.4]).

For the *concept* phase of the development, in which requirements need to be elicited and consolidated, the proposed process supported by formal methods foresees the following phases:

- Requirements Elicitation and Simulation: for which Simulink-Stateflow was selected as

appropriate tool to provide a rigorous, complete modelling of the integration of the Moving Block with

ATO, and to produce a requirements specification for the integrated system;

- **Mapping to Formal Languages:** for which UML was chosen as intermediate language towards a formalisation into Event-B;

- Formal Verification: for which ProB was chosen as formal tool to verify the requirements against the Event B model.

The proposed process was applied to the modelling and verification of the Moving Block with ATO. First, two separate Simulink-Stateflow models were developed for the Moving Block and the ATO, based on a set of preliminary requirements. The requirements were then extended and consolidated based on the simulation, an integrated model was developed and a final integrated requirements specification was produced. The models are reported at [25]. Instead, the requirements are reported in the Annex A – System Requirements.

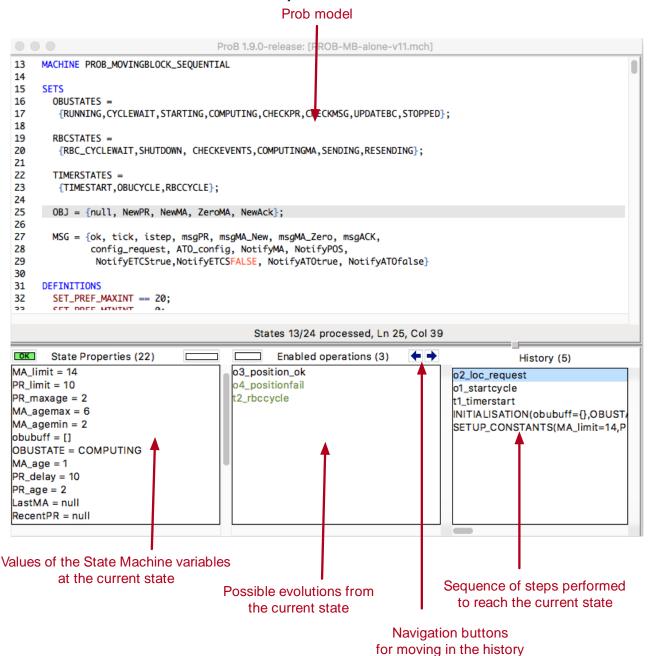

The model and the requirements were used as input to define a UML model oriented to have a clear, established specification that could be used as a reference for translation into formal languages. The UML model was translated into EventB, the formal input language of ProB. The graphical UML model is reported in this deliverable, while the ProB model is available at [25].

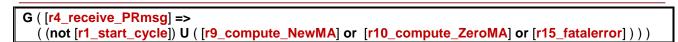

Given the EventB model that integrates Moving Block and ATO, formal verification activities were carried out with the ProB tool. Specifically, part of the requirements reported in the Annex A – System Requirements were mapped to Linear Temporal Logic (LTL) formulae, and model checking was performed with ProB.

The implementation of the process and its application to the Moving Block with ATO has showcased strong points and weaknesses of the applied strategy. Specifically, the main strengths are:

- 1. Modelling and simulating with Simulink-Stateflow enables the identification of incomplete, inconsistent, or too generic requirements, as it forces the modeller to take implementation choices, and allows the user to observe the behaviour of the system and interact with it.

- 2. Graphical models are easy to understand by domain experts, and reading Simulink-Stateflow models required limited guidance, therefore making the language suitable for interaction between formal methods experts and railway domain experts.

- 3. The UML modelling activity enables the abstraction from concrete choices required by the Simulink-Stateflow platform, and, in particular, allows the modeller to observe nondeterministic behaviour.

- 4. The translation of the UML model into Event B enables the further activities of formal verification, but allows also the modeller to identify mistakes in the design.

- 5. The translation of the requirements into temporal logic formulas to be verified again allows the identification of mistakes in the model or in the requirements.

- 6. The formal verification activity can be performed with acceptable, though not negligible, time for most of the requirements.

Instead, observed weaknesses to consider are:

- 1. The modelling and translation processes are time consuming with respect to defining a requirements document in natural language.

- 2. The produced models, although consolidated and revised multiple times throughout the process, are not guaranteed to be stable, as new requirements may emerge during further refinements.

- 3. The formal methods experts must make choices both in the modelling phase and in the translation activities. These choices, concerning for example the decision of modelling subsets of the system to enable formal verification, require the expertise in formal methods and cannot be automatically performed with the selected tools.

- 4. Depending on their nature, part of the requirements could be not formally verified, and require other means to assess them.

5. The whole proposed process is not entirely supported by tools. In particular, the translation activities are performed manually.

Given these observations, the proposed formal process cannot be considered as a fully automated technique. However, the different steps involved, the different languages used, and the different degree of formality of the different steps enabled the possibility of producing a set of consolidated requirements for the integrated Moving-block and ATO system as well as verifiable specifications of the requirements in the form of formal and semi-formal models.

The remainder of the deliverable is structured as follows:

- 1. In Section 2 we present the overview of how the formal methods choices have been validated within ASTRail:

- 2. In Section 3 we present the activity of modelling and simulating with Simulink-Stateflow;

- 3. In Section 4 we present the activities of translation into formal models, through UML and Event B, and formal verification with ProB;

- 4. In Section 5, we report conclusion and final remarks.

### 1.3 Related documents

| ID     | Title                                                                                                                         | Reference | Version | Date       |

|--------|-------------------------------------------------------------------------------------------------------------------------------|-----------|---------|------------|

| [RD.1] | D4.1 Report on Analysis and Ranking of Formal methods                                                                         | D4.1      | 4.2     | 17/01/2019 |

| [RD.2] | D2.1 Modelling of the moving block signalling system                                                                          | D2.1      | 2.0     | 28/01/2019 |

| [RD.3] | D2.2 Moving Block signalling system Hazard Analysis                                                                           | D2.2      | 2.0     | 28/01/2019 |

| [RD.4] | D <sub>3.2</sub> Automatic Train Operations: implementation, operation characteristics and technologies for the Railway field | D3.2      | 1.2     | 28/01/2019 |

| [RD.5] | D4.2 Preliminary Trial Report                                                                                                 | D4.2      | 1.1     | 27/11/2018 |

# 2 Validation of the Process

This section describes the methodology followed to validate the proposed process to select and adopt formal methods in the railway context. Specifically, we first explain how we selected a subset of the available formal methods, and how we have used them for different purposes, namely requirements elicitation and simulation, and formal verification.

It is worth highlighting that the process outlined is applied in the *concept* phase of the development process, in which early requirements are defined and preliminarily validated. It is outside the scope of this deliverable to present a full formal process from early requirements to implementation. Our goal is instead to highlight how the features of diverse tools can be exploited for different purposes.

#### 2.1 Formal methods selection

In this section we present how we have leveraged the information from the previous deliverables, namely D4.1 and D4.2, to select the appropriate formal methods to use in our context. Specifically, we justify why we have chosen Simulink-Stateflow for requirements elicitation and consolidation, and why we have selected UML as intermediate representation and ProB for formal verification. In the following, we first outline the most relevant information from previous deliverables, and then we motivate our choices.

# 2.1.1 Main Output from Previous Deliverables

In this section, we list the main output from the previous deliverable that we considered to support the selection of formal methods for our specific context.

In D4.1, we performed a literature survey on formal methods applications to railway problems, complemented with a review of projects, a questionnaire with practitioners and a preliminary tool evaluation. One of the main output from D4.1, also published in [20] and [21], is the **dominance of the B method** and associated supporting tools (Rodin environment, Atelier B, ProB) in the railway context.

In D4.2, we performed a tool trial, by modelling a preliminary specification of the moving-block system with fourteen formal tools, selected based on the survey from D4.1. Furthermore, we performed a usability test for the eight selected tools. Despite the dominance of the B method in literature and practice, D4.2 has shown that each method and associated tool is **appropriate for different development contexts**. Specifically, one of the main conclusions from D4.2 was as follows:

- Simulink and SCADE are appropriate for both early prototyping and detailed design towards code generation, other tools need to be used when aiming at formal verification.

- UMC is appropriate for initial prototyping, when one wants to adopt a design based on UML state machines to facilitate communication with different stakeholders, but wants also verification capabilities as the ones provided by UMC.

- Uppaal is appropriate when one needs to focus on the verification quantitative, real-time properties and probabilistic aspects.

- NuSMV and SPIN are appropriate when the system, or composition of systems, has a large state space, and one needs to verify temporal logic properties.

- Atelier B and ProB are the right choice for top-down development (i.e., from initial design to code) of single systems, and have somewhat complementary verification capabilities, with Atelier B supporting invariants checking, and ProB supporting model checking.

Other tools, although not widely used in railways, such as CADP and FDR4, have been also experimented in the context of the project and demonstrated their appropriateness for the modelling and verification in the context of large scale, systems of systems.

Finally, another output from D4.2, concerning **usability** of formal tools, as evaluated by railway practitioners in the context of the project, is that tools that offer graphical simulation capabilities such as Simulink, SCADE, ProB and Uppaal are considered more usable, and easy to understand by practitioners.

#### 2.1.2 Choice of Formal Methods based on the Development Context

As mentioned, the current context is the *concept phase* of the development. In this phase, requirements for the moving-block system and the ATO need to be (1) elicited from stakeholders and documentation, (2) preliminary assessed with formal verification.

Therefore, we have chosen Simulink (and its package for state machines modelling, named Stateflow) as a means to support the requirements elicitation task of this phase. Although also SCADE would have been an appropriate choice according to the conclusions reported above, we selected Simulink since, from our tool usability evaluation presented in D4.2, the tool was considered the most usable by the participants (System Usability (SUS) Score: 76 over 100). Since in the early phase of elicitation it is crucial that all the involved stakeholders, namely formal methods experts and railway experts, understand the language used for modelling, Simulink was considered as a suitable choice for our project.

Concerning formal verification of the requirements, i.e., verification of qualitative properties related to conditions and expected actions, we have selected ProB as the main tool given (a) the dominance of this tool in the railway context, as outlined by D4.1, and (b) it evaluation in terms of usability as shown in D4.2 (SUS Score: 62 over 100, ranked third in terms of usability right after Simulink and SCADE).

# Formal Methods Application Process

In this section we provide an overview of the application of the formal process, based on the selected formal methods and tools. The output of the process in terms of models is further detailed in Sect. 3 and 4.

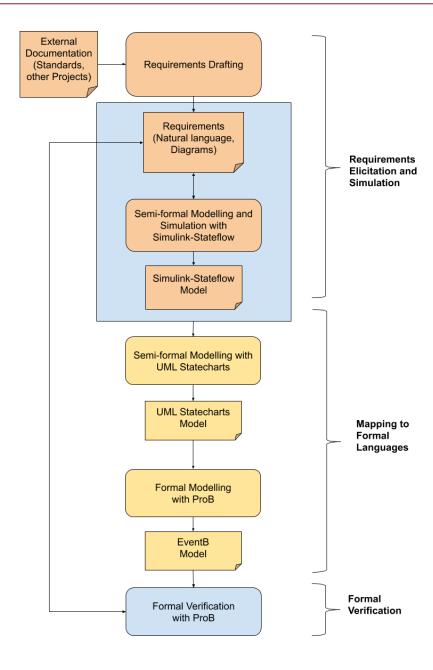

Figure 1 outlines the adopted formal process. The starting point of the process is a set of input documents about the systems to be developed (External Documents). Specifically, in our context, we leveraged the preliminary requirements of the moving-block system developed in D4.2, and the requirements for the ATO system available from the Shift2Rail X2Rail-1 deliverable D4.1 - ATO over ETCS GoA2 Specification [26]. These documents were used as a source to draft the first early requirements for the moving-block and ATO systems (Requirements Drafting). The produced requirements, expressed in natural language and complemented with informal models, were then represented and simulated by means of Simulink-Stateflow (Semi-formal Modelling and Simulation with Simulink-Stateflow). This activity allowed to further elicit, refine and improve the drafted requirements towards a stable requirements document.

The produced Simulink-Stateflow model together with the produced requirements were used as a starting point for formal verification. To enable verification, the requirements expressed through the model were first represented into an intermediate format, namely UML Statecharts (Semi-formal Modelling with UML Statecharts). The goal was to have an intermediate model expressed in a format from which different, comparable formal models could be potentially derived. We have chosen to use UML Statecharts as UML is the most common language for representation of systems in railways, as shown by the results in D4.1. From the UML Statecharts model, a formal ProB model was derived (Formal Modelling with ProB). Qualitative formal verification was then performed on this model, based on the requirements defined earlier. The verification allows to assess the requirements and possibly improve them (Formal Verification with ProB). The UML model can also be used as a starting point to derive other models, and practice formal methods diversity, by comparing the results obtained with other tools.

Figure 1 Overview of the adopted formal process

# 2.2.1 Requirements Elicitation and Simulation

In this section we outline the process followed to provide the models for the moving-block and the ATO, and to define the final set of requirements for the two components, including systems integration elements.

**Moving-block:** the moving-block requirements were preliminarily defined as part of D4.2. During the current task of ASTRail, the preliminary requirements were further refined and simulated by means of Simulink-Stateflow. Specifically, representative formal methods experts from CNR developed the Simulink-Stateflow model based on the requirements reported in D4.2. Whenever a requirement was considered inconsistent, incomplete, or unclear, based on the modelling and simulation activities, reported back the problem to the railway domain experts from SIRTI. The interaction was aided by the graphical models presented to the

experts from SIRTI, who took care of updating and modifying the original requirements, based on the reported problems. At the end of these iterations, a novel requirements document was produced for the moving-block system. The document is reported in Annex A – System Requirements – Part 1, Moving Block.

**ATO:** the initial ATO requirements come from the Shift2Rail X2Rail-1 deliverable D4.1 - ATO over ETCS GoA2 Specification [26]. Differently from the moving-block requirements, these are very detailed, and a complete model of them was considered out of the scope of the current project. Therefore, in this case, the railway experts from SIRTI selected a subset of the requirements that could be suitable to produce a model to be integrated with the moving-block model. These initial requirements were modelled, simulated and refined with the same approach used for the moving-block system, i.e., by means of multiple iterations and discussion between CNR and SIRTI. The document is reported in Annex A – System Requirements – Part 2, ATO.

**Integrated System:** following the definition of the requirements for moving-block and ATO, an integrated Simulink-Stateflow model was produced by CNR. This model was used as a baseline to define the final requirements concerning the interaction between ATO and moving-block. These final requirements, developed by SIRTI, are reported in Annex A – System Requirements – Part 3, Integrated System.

## 2.2.2 Mapping to Formal Languages

In this section we outline how the original model and requirements for the **Integrated System** were mapped into the ProB input language, named ProB, to enable verification. This activity involved modellers from CNR and representative of SIRTI, to adjust the requirements previously produced.

For the mapping towards EventB, a first modelling by means of the UML language was performed by CNR. This modelling activity took into account the requirements produced, and reported in Annex A – System Requirements, together with the integrated Simulink model (Annex A – System Requirements – Part 3, Integrated System). The modelling abstracted away from quantitative aspects that were not relevant for the foreseen type of formal verification. After the UML representation, an EventB model was defined as a faithful mapping of the UML model, to enable formal verification. The mapping activity, together with the UML model and EventB model, is reported in Section 4 together with the formal verification activity introduced in the next section.

It is worth mentioning that the model produced in UML, and translated into EventB, is not a faithful translation of the original Simulink-Stateflow model. Indeed, the goal of this model is to enable the analysis of relevant requirements aspects, and not to verify the original Simulink-Stateflow design, which was oriented towards the elicitation of the requirements. This opportunistic and non-systematic approach to modelling and verification is considered appropriate for this concept phase, to clarify whether the elicited the requirements are reasonable.

## 2.2.3 Formal Verification

In this section we outline the process followed verify the components from a quantitative and qualitative point of view. This verification activity was oriented to showcase the process, to demonstrate that the system specification produced, i.e., the requirements and the Simulink-Stateflow model, is *verifiable*, as originally planned in the DoW. The formal verification was performed by means of the ProB tool. To this end, part of the requirements reported in Annex A – System Requirements were considered and translated into linear temporal logic (LTL) formulas. The translation process, results and comments are reported in Section 4.3.

# Moving Block and ATO modelling

In this section we provide a description of the moving block and ATO Simulink models developed, based on the process described in Sect.2.2.1. We first describe some basic principles of the Simulink and Stateflow languages, which are useful to understand the rest of the section. Then, we present each model individually, and we describe the final, integrated model, pinpointing the adjustments needed to complete the integration. At the end of the section, we discuss observations throughout the process of requirements elicitation and simulation.

# 3.1 Simulink and Stateflow Languages

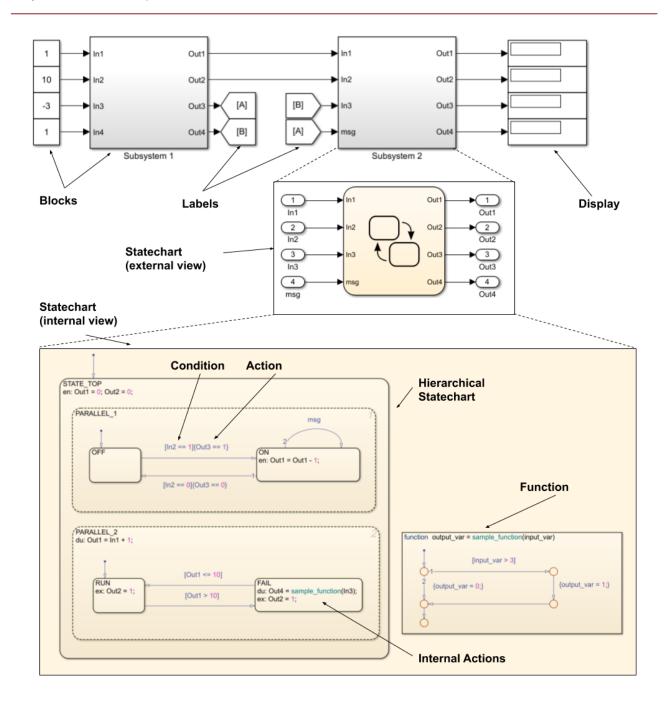

Simulink is a commercial model based development tool, distributed by Mathworks, that allows the user to graphically draw diagrams of the system modelled in the form of input-output blocks. The blocks can be further refined in the form of hierarchical state machines through the tool Stateflow, included in Simulink. Simulink comes with several packages, also for code generation from the models. For the current models, we used **Simulink 2017b**. Below, we present some basic concepts about the Simulink and Stateflow languages, useful to interpret the models presented in the following sections. For more details, we refer to the extensive Simulink documentation [2]

Figure 2 Simulink and Stateflow basic concepts

- **Simulink Blocks:** a sample Simulink diagram is represented in Figure 2 (top). The basic elements of Simulink are the **blocks**, which are components that take some input and produce some output. Each component in Simulink, including elements with several input and output variables, is considered a block. Blocks can communicate with direct links, or through labels. Labels with the same name are associated to the same variables or messages exchanged between blocks. In the Simulink diagrams that we will consider in this deliverable, the main blocks are **sub-systems** blocks, i.e., complex blocks with several input and output variables. To observe the status of the different variables during the simulation, one can use specific scope blocks.

- Stateflow Statecharts: subsystems can have different forms, and can include several blocks. In our context, each sub-system is a Stateflow statechart (or Chart, in Stateflow dialect). Figure 2 (bottom)

represents a sample statechart. The statechart inherits input and output from the associated subsystem block. Furthermore, it is composed by a set of hierarchical states. The decomposition of states can be parallel (dashed lines, PARALLEL\_1 and PARALLEL\_2) or mutually exclusive (solid line, for example OFF, ON). Parallel states are actually executed in a sequential order, and the order is visually specified on the chart itself (top-right corner of each parallel state).

- Conditions and Actions: Conditions and actions can be used in the transitions from mutually

exclusive states. Conditions are expressed in squared brackets, and actions are expressed in curly

brackets. Conditions are normally associated to variables. However, they can also refer to the

reception of messages. In this case they do not make use of square brackets.

- Internal Actions: Actions can be defined also within the states. There are three types of actions: entry actions (en), which are executed only once when the system enters the specific state; during actions (du), which are executed at each simulation step; exit action (ex), which are executed when the system exists the state.

- Functions: functions are graphical flowcharts, with conditions and actions analogous to those used for transitions between states. Functions can be called within actions in states, in transitions, and in functions themselves. The main difference between a function and a statechart with mutually exclusive states is that a function is entirely executed within one simulation step, while at each simulation step only one state in a certain hierarchy can be active in a statechart. This is similar to the difference that we have between a C function with nested if-then-else statements, and a C function with a switch case statement. The former is analogous to Stateflow functions. The latter is analogous to Stateflow statecharts with mutually exclusive states.

### 3.2 Moving Block

### 3.2.1 Moving Block Overview

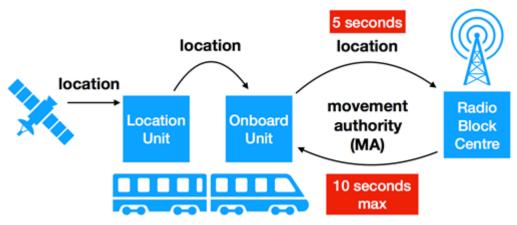

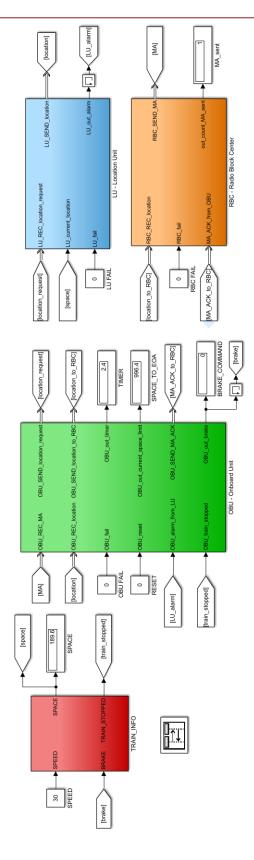

The components of the moving block system considered are depicted in Figure 3. The train carries the Location Unit (LU) and OBU (On-board Unit) components, while the RBC (Radio-block Centre) is a trackside component. The LU receives the train's location from GNSS satellites, sends this location (and the train's integrity) to the OBU, which, in turn, sends the location to the RBC. Upon receiving a train's location, the RBC sends a Movement Authority (MA) to the OBU (together with speed restrictions and route configurations), indicating the space the train can safely travel based on the safety distance with preceding trains. The RBC computes the MA by communicating with neighbouring RBCs and by exploiting its knowledge of the positions of switches and other trains (head and tail position) by communicating with a Route Management System (RMS). In our context, we abstract from an RMS and communication among neighbouring RBCs: we consider one train to communicate with one RBC, based on a seamless handover when the train moves from one RBC supervision area to an adjacent one, as regulated by its Functional Interface Specification [1]. Next to these physical components, there are two temporal constraints for the OBU to respect: the location is continuously updated every 5 seconds, whereas the MA must be continuously updated within 10 seconds. If the OBU does not receive an MA within 10 seconds from the last MA, the OBU is required to force the train to brake

Figure 3 Overview of the Moving-block system

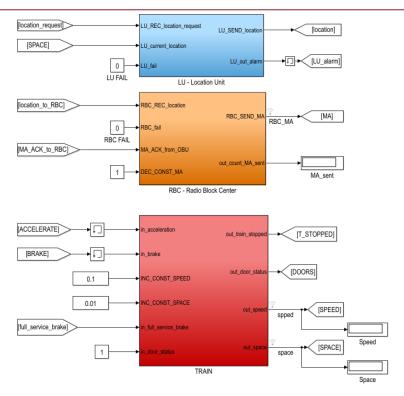

# 3.2.2 Moving-block Model Architecture

Figure 4 reports the architecture of the model, which includes four main Simulink blocks representing the interacting subsystems, namely OBU, LU, RBC, and Train. Each block communicates with the other blocks by means of input/output messages. For example, the label named **location** is one of the outputs of the LU, and it is input to the OBU block. This indicates a virtual channel by which a message is exchanged between LU and OBU, including the current train location. Similarly, **location\_to\_RBC** is one of the outputs of the OBU block, also serving as input to the RBC block: the OBU location, received from the LU, is passed to the RBC, which, in turn, can compute the MA and send it to the OBU. The OBU is also in charge of activating the brake, and the brake's status can be visualised in the **BRAKE\_COMMAND** scope element. Similarly, other scope elements are used to visualise a TIMER, indicating the time from the last received MA (2.4 seconds in Figure 4), and **SPACE\_TO\_EOA**, which is the space from the current position to the end of the MA (996.4 meters). Following the requirements, failure inputs (**OBU\_FAIL**, **RBC\_FAIL**, and **LU\_FAIL**) are associated to each block to simulate external events that may trigger system failures.

In the following sections we describe the behaviour of the different components of the model, namely OBU, LU, RBC and Train.

Figure 4 Architecture of the Moving-block Simulink Model

# 3.2.3 Behaviour of the Moving-block System: OBU Component

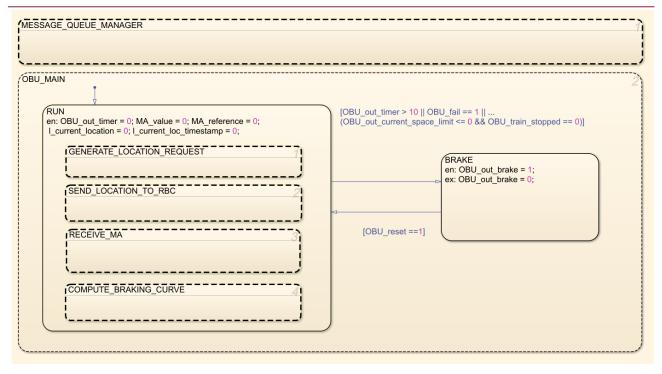

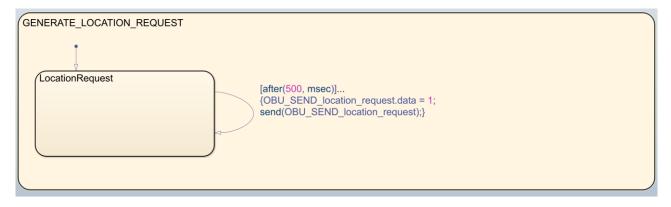

Figure 5 reports a high-level view of the behaviour of the OBU component. The model has two main parallel states: **MESSAGE\_QUEUE\_MANAGER** and **OBU\_MAIN**.

**MESSAGE\_QUEUE\_MANAGER**, which appears in all the developed Simulink models, handles the queue of received messages. Specifically, at each clock cycle the queue is emptied, and only the last message received is read and processed. The internal part of the state is not reported in the picture, as this parallel state has solely an ancillary role for the model.

**OBU\_MAIN** represents the main behavioural block of the OBU is composed of a statechart of two states, **RUN** and **BRAKE**. The system passes from the normal state RUN to the BRAKE state whenever the timer set to receive a movement authority (**OBU\_out\_timer**) exceeds 10 seconds, or there is a failure (**OBU\_fail** == 1) or the train is moving and the current space limit is exceeded, i.e., the MA has been violated. The system can return to the RUN state only upon reset (**OBU reset** == 1).

The RUN state is itself composed of parallel states that handle the different functions of the OBU. Specifically, four states are considered, and described in the following.

- GENERATE\_LOCATION\_REQUEST (Figure 6). Every 500 milliseconds (see condition after(500, ms)) a location request message is sent to the LU.

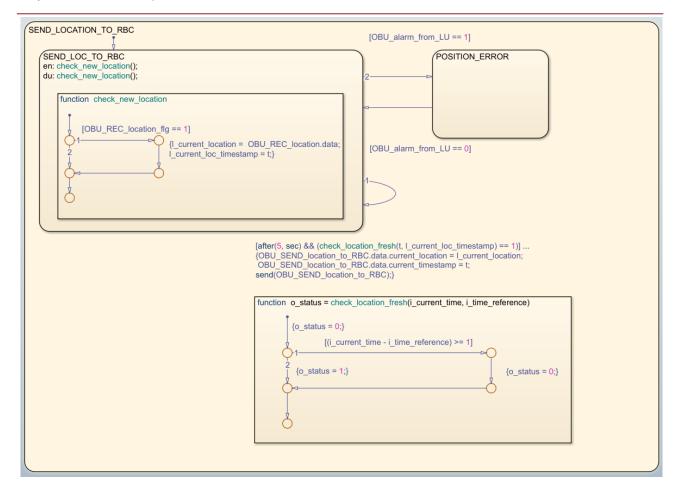

- SEND\_LOCATION\_TO\_RBC (Figure 7). At every cycle, the sub-state SEND\_LOC\_TO\_RBC controls whether a new location is received from the LU (function check\_new\_location). Then, every 5 seconds (see condition after(5, sec)) a position report including the current location is sent to the RBC. This happens only if the location received is not older than 1 second (function check\_location\_fresh). In case an alarm is received from the LU, the statechart goes to the state POSITION\_ERROR. From this state, no update is sent to the RBC. As a consequence, no MA will be received, and the system will eventually brake thanks to the 10 seconds timeout (OBU\_out\_timer > 10 in Figure 5).

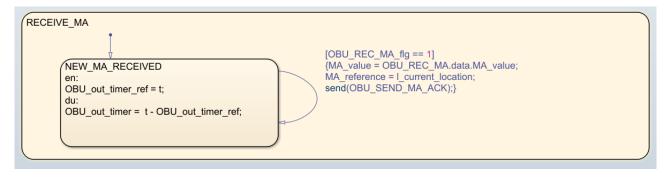

- RECEIVE\_MA (Figure 8). If a new MA is received from the RBC (OBU\_REC\_MA\_flg == 1), the current MA value is updated, and an ACK message is sent to the RBC.

- COMPUTE\_BRAKING\_CURVE (Figure 9). At every cycle, the space to the end of authority is computed based on the current MA value (MA\_value), the location in which the MA was received (MA\_reference), and the current location (I\_current\_location). The space to the end of authority is represented by the variable OBU\_out\_current\_space\_limit. This represents a form of braking curve in the current instant, expressed in terms of space. The actual computation of the braking curve in terms of speed, and taking into account the train weight and other parameters that depend on the line, is not considered in the current model, as its main focus is on the interaction between the different components and not on a faithful implementation of all the details of the control system.

Figure 5 Behaviour of the OBU component: High-level view

Figure 6 Behaviour of the OBU Component: GENERATE\_LOCATION\_REQUEST State

Figure 7 Behaviour of the OBU Component: SEND\_LOCATION\_TO\_RBC State

Figure 8 Behaviour of the OBU Component: RECEIVE\_MA State

```

COMPUTE_BRAKING_CURVE

en: OBU_out_current_space_limit = get_current_space_limit(MA_value, MA_reference, I_current_location);

du: OBU_out_current_space_limit = get_current_space_limit(MA_value, MA_reference, I_current_location);

function o_current_space_limit = get_current_space_limit(i_MA_value, i_MA_reference, i_current_location)

{o_current_space_limit = i_MA_value + i_MA_reference - i_current_location;}

```

Figure 9 Behaviour of the OBU Component: COMPUTE\_BRAKING\_CURVE State

# 3.2.4 Behaviour of the Moving-block System: LU Component

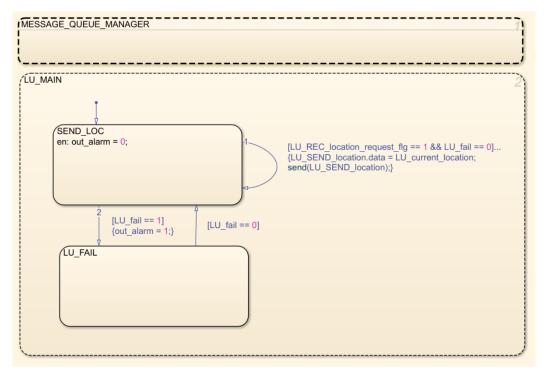

Figure 10 represents the behaviour of the LU component. Besides the support state MESSAGE\_QUEUE\_MANAGER, which handles the message queue, and was already described in Section 3.2.3, we have a main state called **LU\_MAIN**. This is composed of two sub-states: **SEND\_LOC** and **LU\_FAIL**. The former sends a position report message including the current location of the train, every time a request is received from the OBU (**LU\_REC\_location\_reques\_flg == 1**). Whenever a failure occurs, the LU goes into the LU\_FAIL state, and raises an alarm, which is received by the OBU (**out\_alarm == 1**).

Figure 10 Behaviour of the LU Component

# 3.2.5 Behaviour of the Moving-block System: RBC Component

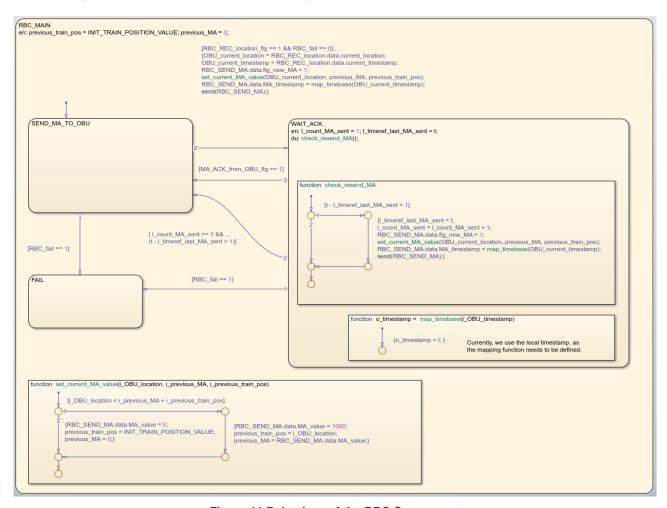

Figure 11 represents the main behaviour of the RBC system (here, we do not report the MESSAGE\_QUEUE\_MANAGER state, for ease of visualisation). The system has three states, namely: **SEND\_MA\_TO\_OBU**, **WAIT\_ACK** and **FAIL**.

In the state SEND\_MA\_TO\_OBU, whenever a new location is received (RBC\_REC\_location\_flg == 1) and no failure occurred, a message called RBC\_SEND\_MA to be sent to the OBU is composed. Such message includes the MA value for the OBU, which is computed by means of the **set\_current\_MA\_value** function.

This function, reported at the bottom of the figure, takes into account the current location of the train, the previous MA value sent, as well as the previous train position (OBU current location, previous MA, previous train pos). If the current location of the train does not appear to violate the old MA, a new MA value is sent, always equal to 1000 meters, for the sake of simplicity. Instead, if the train appears to have violated the MA, a message is sent to the OBU including an MA value equal to 0, so that the train is forced to brake.

After sending the message to the OBU, the RBC goes into the WAIT\_ACK state. If an ACK is received (MA\_ACK\_from\_OBU\_flg == 1), the RBC goes back to the initial state and waits for another position report from the OBU. If an ACK message is not received, the RBC remains in the WAIT\_ACK state, and sends again the message after one second from the previous one (see function check\_resend\_MA). This is repeated for three times maximum. Then, if no ACK is received from the OBU, the system goes back to the initial state (see transition I\_count\_MA\_sent >= 3).

Figure 11 Behaviour of the RBC Component

#### Behaviour of the Moving-block System: Train Component 3.2.6

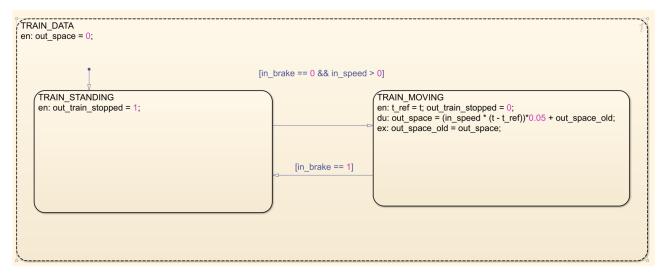

Figure 12 reports a simple statechart that represents the train behaviour, and it was introduced for simulation purposes, as the train is not strictly part of the moving-block system, but it belongs to the controlled environment. Hence, the one presented is not a faithful train model, but rather a model that enables the whole moving-block system to be simulated, with variations of speed and space, based on user's input and on the brake activated by the OBU (variable in\_brake). From the architecture view (Figure 4), the user can select the current speed of the train, and set the value for the in\_speed variable, coming from the SPEED parameter (set to 30 in Figure 4). The statechart includes two states: TRAIN\_STANDING and TRAIN\_MOVING. In the second state, the location of the train (variable out\_space) is computed based on

the selected speed and the location of the train when the train was standing (out\_space\_old). The constant parameter 0.05 is used simply to adjust the simulation and has not physical meaning.

Figure 12 Behaviour of the Train Component

#### **ATO** 3.3

#### **ATO Overview** 3.3.1

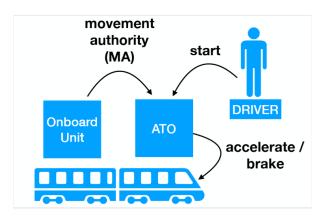

Figure 13 depicts the automatic train operation system (ATO) and the contextual elements of the environment with which the ATO system interacts. Specifically, we have a train DRIVER, the ETCS Onboard Unit (called OBU, in the following), which is the on-board automatic train protection (ATP) system, and the TRAIN.

The OBU interacts with the ATO to send information about certain external conditions, configuration data, as well as the values of the MA received from the RBC. In our simplified context, the MA values represent also the missions of the ATO. In a more realistic context, missions and MA would be separated.

The DRIVER is in charge of starting the automatic driving mode of the ATO. In this mode, the ATO accelerates the train until a certain target speed, and then brakes the train sufficiently in advance before the end of the MA received from the OBU. We will see that in the integrated model, presented in Section 3.4 all accelerate and brake commands will pass through the OBU. However, at this stage, it is assumed that the ATO has full control of the train.

Figure 13 Overview of the ATO in its context

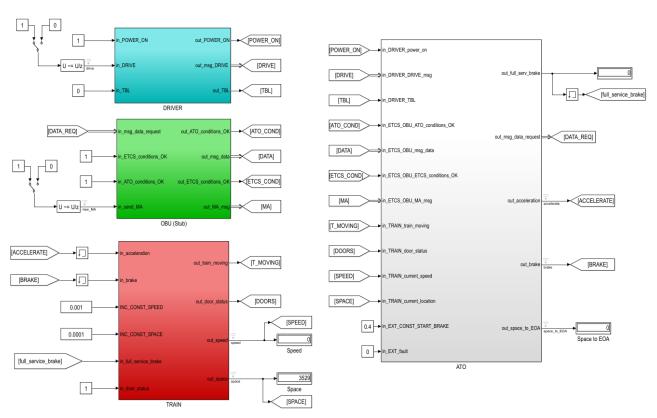

# 3.3.2 ATO Model Architecture

Figure 14 represents a high-level view of the ATO component (light grey block) in its environment. The environment is composed of three components:

- DRIVER (cyan block), which starts the ATO system (label POWER\_ON), commands the automatic

driving function (label DRIVE), and activates the train brake lever (label TBL). These commands are

set by the user, and forwarded to the ATO.

- OBU (Stub) (green block), which is a simplified version of the OBU considered in the moving-block system from Section 3.2, and limited to those functionalities that are relevant for the ATO, namely sending the movement authority (label MA), setting the status of the external conditions that allow the ATO to change its internal states (ATO\_COND, ETCS\_COND), and sending data configuration messages (DATA) when requested by the ATO at start-up (DATA\_REQ).

- TRAIN (red block), which is again a representation of the train dynamics, although slightly more complex with respect to the one used for the moving-block system and presented in Section 3.2.6. Indeed, the block takes as input the acceleration and braking commands coming from the ATO (ACCELERATE, BRAKE, full\_service\_brake), and changes Speed and Space accordingly. Two parameters (INC\_CONST\_SPEED, INC\_CONST\_SPACE) are used as input to enable a realistic simulation.

The ATO component takes input from the different elements of the environment and produces output, mainly towards the TRAIN component. Besides the input to the ATO already mentioned above, the ATO has also two external input variables, which are <code>in\_EXT\_CONST\_START\_BRAKE</code>, a parameter to decide when the system shall start braking with respect to the end of the MA (currently arbitrarily set to 0.4), and <code>in\_EXT\_fault</code>, which simply injects a failure in the ATO system.

Figure 14 Architecture of the ATO Model

In the following section, we describe the internal behaviour of the ATO block, including also some details of the TRAIN block that are relevant to understand the ATO behaviour.

The DRIVER and OBU components of the environment are used only for simulation purposes, to enable debugging and simulation of the ATO behaviour, and therefore their internal behaviour is not reported here.

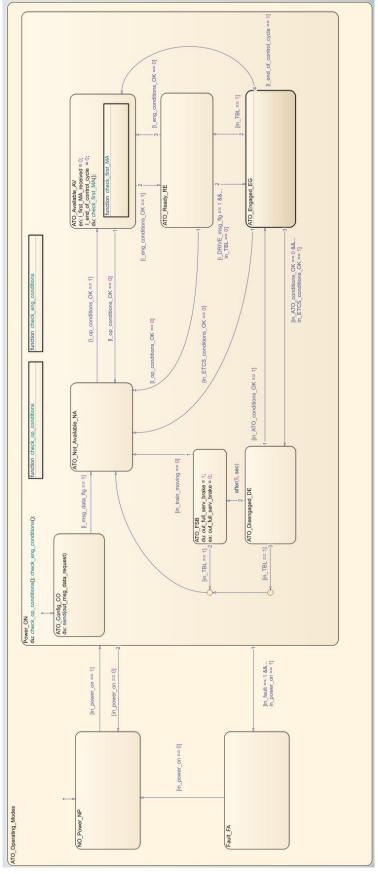

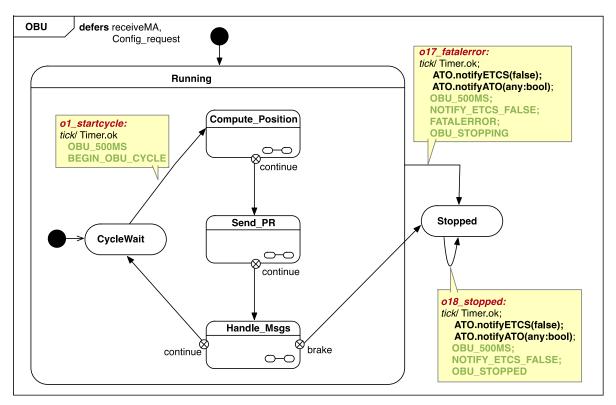

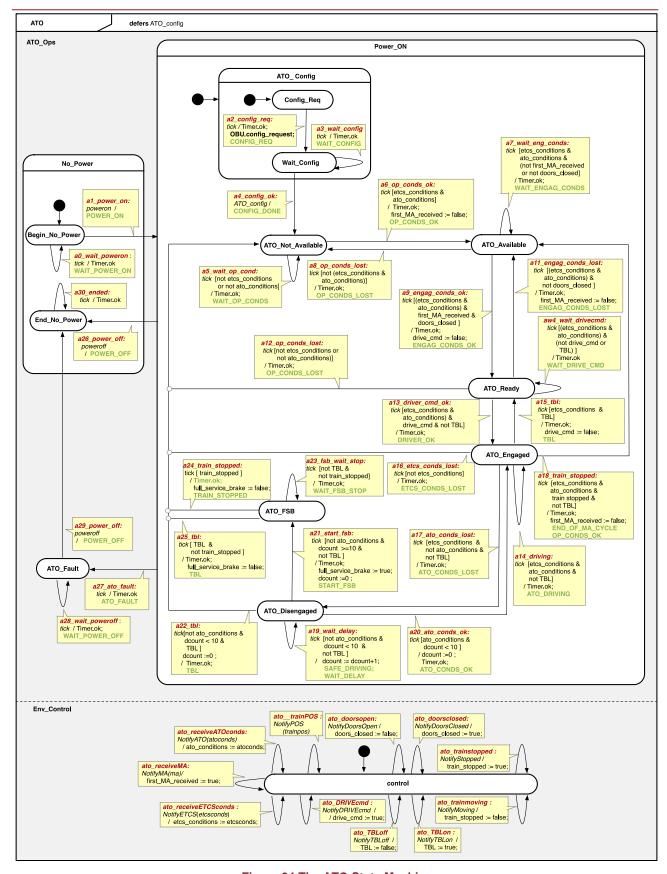

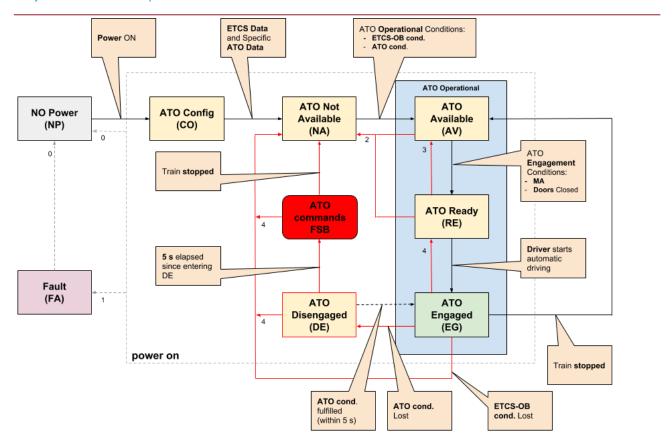

# 3.3.3 ATO Behaviour: Operating Modes

Figure 15 reports the main statechart of the ATO named ATO\_Operating\_Modes, which controls the changes of ATO operating modes, based on external conditions (as for the other models, also in this case we have a MESSAGE\_QUEUE\_MANAGER block, but it is not reported in the figure). The statechart has three main states, namely **NO\_POWER\_NP** (representing the initial status of the system when it is not activated yet by the driver), **POWER\_ON** (state of activation) and **FAULT\_FA** (state of fault due to external conditions).

In the POWER\_ON\_STATE, the ATO system starts from the configuration state (ATO\_CONFIG\_CO), and requests the data to the OBU. When the data is received (I\_msg\_data\_flg == 1), the system goes to ATO\_Not\_Available\_NA. If the operational conditions are fulfilled, the system goes to ATO\_Available\_AV. Note that the operational conditions are fulfilled when both the ATO and ETCS conditions coming from the OBU (ATO\_COND, ETCS\_COND already mentioned in Figure 14) are fulfilled, and this is controlled by the check\_op\_conditions function in Figure 15. From the ATO\_Available\_AV state the system goes to the ATO\_Ready\_RE state, if the engagement conditions checked by the function check\_eng\_conditions are also fulfilled.

From the ATO\_Ready\_RE state, the system goes to the **ATO\_Engaged\_EN** state upon external command coming from the DRIVER block. This external command identified by the variable **I\_DRIVE\_msg\_flg**, which is a local variable linked to the DRIVE label from Figure 14. The internal part of the ATO\_Engaged\_EN state, which is the main state of the ATO and is concerned with the automatic driving of the train, will be described in Section 3.3.4.

From the ATO\_Engaged\_EN state, the system can move to three states: back to the ATO\_Available\_AV when its mission is finished (I\_end\_of\_control\_cycle == 1); back to the ATO\_Not\_Available\_NA, in case ETCS conditions are not fulfilled anymore; to the ATO\_Disengaged\_DE state if only the ATO conditions are lost, but the ETCS conditions are still fulfilled. In case ATO conditions are restored within 5 seconds, the system goes back to the ATO\_Engaged\_EN state, otherwise the system starts the full service brake going to the ATO\_FSB state. When the train is standing (in\_train\_moving == 0), the system goes back to ATO\_Not\_Available\_NA. This state is also reached if the driver activates the TBL, hence taking charge of braking the train.

Note that the ATO system does not activate the brake in case ETCS conditions are lost, as the train control should be performed by the OBU in this case.

Figure 15 Statechart representing the Operating Modes of the ATO

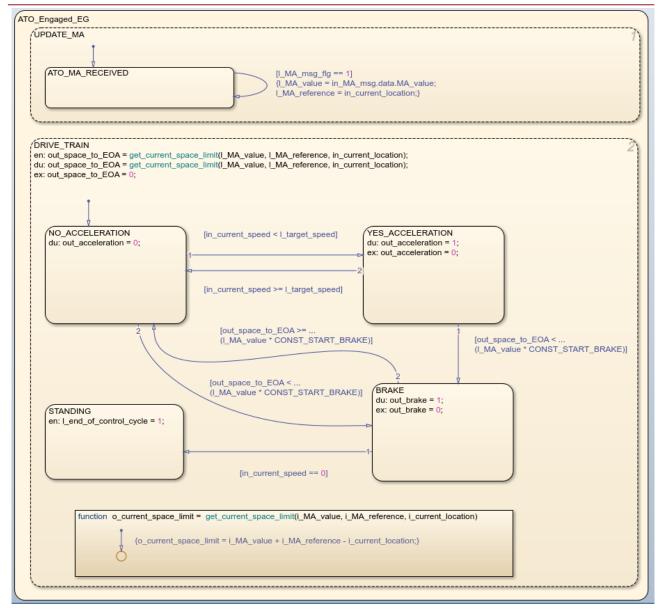

### 3.3.4 ATO Behaviour: Speed Control and Train

In this section we describe how the ATO system controls the train speed, based on the MA messages received from the OBU.

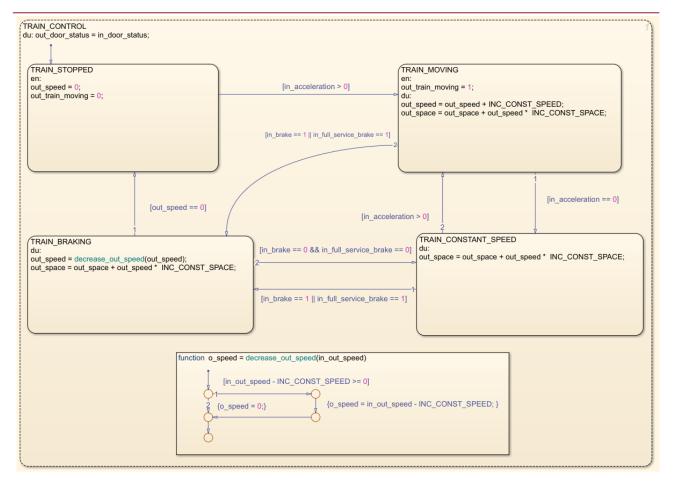

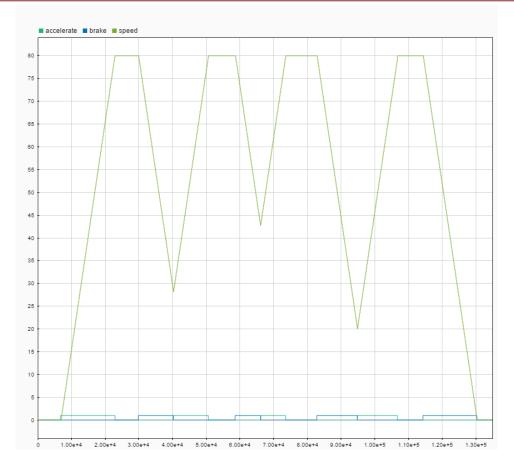

Figure 16 reports the internal behaviour of the engaged state of the ATO, called ATO\_Engaged\_EN. Instead, Figure 17 reports the simple model of the train, which is controlled by the ATO.

The statechart ATO\_Engaged\_EN has two main states, **UPDATE\_MA** and **DRIVE\_TRAIN**. The former takes care of unpacking new MA messages coming from the OBU. The latter is in charge of commanding acceleration (variable **out\_acceleration**) and brake (**out\_brake**) based on the space to the end of the MA (**out\_space\_to\_EOA**) which is continuously computed by the function **get\_current\_space\_limit**, analogous to the one already described in Section 3.2.3, and included in the OBU of the moving-block system. The DRIVE\_TRAIN statechart has four exclusive states: NO\_ACCELERATION, in which the train does not accelerate; YES\_ACCELERATION, which is active until the target speed is reached; BRAKE, which is activated if the space to the end of the MA is lower than a certain rate set by the input parameter **CONST\_START\_BRAKE**; STANDING, which is the final state, reached when the mission is finished, the train is standing, and no new MA is received.

The states in the ATO\_Engaged\_EN statechart have some corresponding states in the statechart that represents the train behaviour in Figure 17. This statechart includes the states TRAIN\_STOPPED, TRAIN\_MOVING, TRAIN\_CONSTANT\_SPEED and TRAIN\_BRAKING, which have an intuitive role. As the model of the train is a simplified version of the actual dynamic of a train, the space and the speed are increased constantly according to the input parameters <code>INC\_CONST\_SPEED</code> and <code>INC\_COST\_SPACE</code> whenever the train is moving. When simulating the model, these parameters shall be adjusted to enable a realistic simulation: they are currently set to 0.001 and 0.0001, but different values maybe set if the simulation is too slow or too fast (this depends on several factors, including the characteristics of the PC used to run the simulation).

Figure 16 Statechart representing the internal behaviour of the ATO Engaged State

Figure 17 Statechart representing the Train model for the ATO

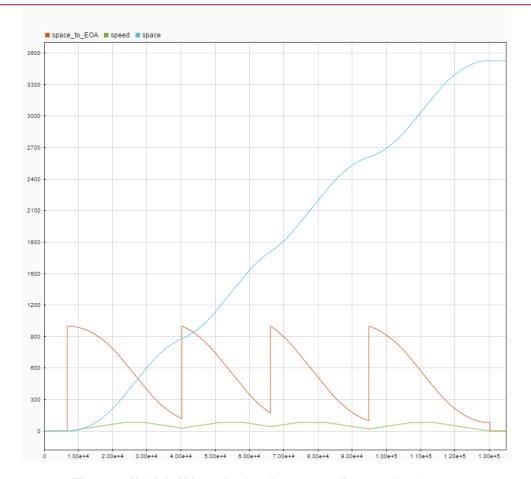

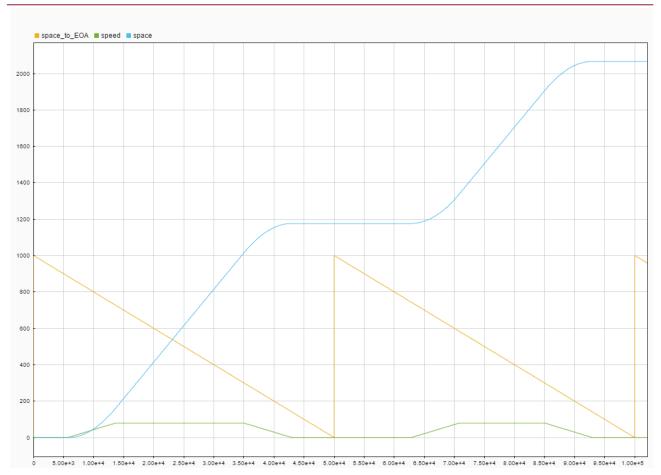

Figure 18 Multiple MA received and corresponding speed and space

To understand the interaction between the different components that appear in Figure 14, and especially the ATO, the OBU (Stub) and the TRAIN, it is useful to look at the scenario reported in Figure 18. The figure shows the **space** crossed by the train, its **speed**, and the variations of the variable **out\_space\_to\_EOA** indicating the space remaining to the end of the MA. In the scenario, four MA messages are received, with a constant value of 1000 meters. At each iteration, the train accelerates until the speed of 80 Km/h is reached, keeps its speed constant and then starts braking when approaching the end of the MA. If a new MA is received, the train starts accelerating again.

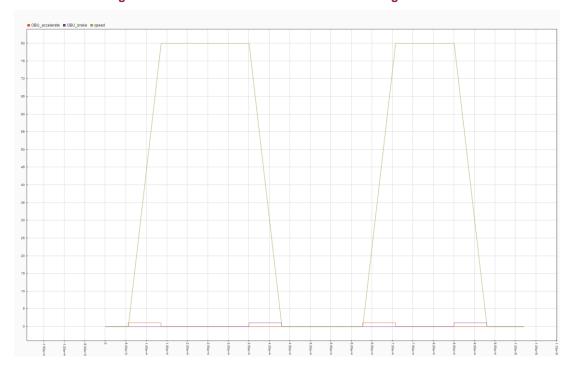

Figure 19 Brake and acceleration commands in relation to the train speed

To better appreciate the variation of speed, in relation to acceleration and brake, it is useful to look at Figure 19, which is associated to the same scenario with the reception of multiple MA messages described above. In the figure, we see that the acceleration command is active until the target speed of 80 Km/h is reached, and the train starts braking after a while to avoid violation of the MA. This process is repeated for four times, i.e., anytime a new MA message is received. At the end, no new MA is received, and the train reaches 0 speed (in Figure 16 this activates the variable <code>l\_end\_of\_control\_cycle</code>). To activate again the automatic driving mode, and enter the ATO\_Engaged\_EN state, a new MA must be received, and the DRIVER block needs to send another <code>DRIVE</code> message to the ATO system (see Figure 14).

# 3.4 Integrated Model

The moving-block system model and the ATO model described in the previous paragraphs were developed independently, and then integrated in a single model. While the initial models maintained their overall nature and structure, adjustments were performed to enable a coherent simulation. In the following, we describe the architecture of the integrated model, and we present scenarios of its behaviour in a typical, successful case, and in case of violation of the MA by the ATO. We do not discuss again the details of the behaviour of the different blocks, as these were already described in the previous sections.

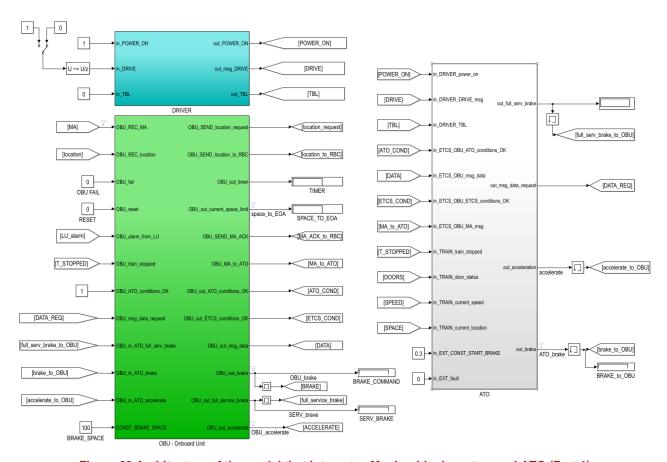

## 3.4.1 Integrated Model Architecture

Figure 20 and Figure 21 report the two parts that compose the overall architecture of the model that integrates moving-block system components and ATO. The DRIVER and TRAIN blocks come from the environment of the ATO model. The ATO block is architecturally equivalent to the original one. The RBC and LU come from the moving-block model. The RBC has been adapted, in that it now includes an additional constant as input, named **DEC\_CONST\_MA**. Such constant value is used to constantly decrease the MA value sent to the OBU during the simulation. The value is decreased every time a new MA is requested. This

was necessary in order to have a realistic simulation in which the MA value changes at each iteration and it is not constantly set to 1000, as in the initial model.

The OBU block is substantially the same as the original one described in Section 3.2.3, with some additional input (DATA REQ, full serv brake to OBU, etc.) that come from the ATO model. Indeed, the OBU is the only component that has a direct control of the TRAIN. All the commands from the ATO (accelerate, braking) are forwarded to the OBU, which in turn forwards them to the TRAIN component. With this architectural solution, the OBU has full control of the train movement.

The OBU also has an additional input named BRAKE\_SPACE. This parameter indicates the number of meters (100, in the figure) before the end of the MA that the system should consider to start emergency braking. This happens only when the ATO fails to control the train, and does not brake sufficiently in advance. Such a scenario can be triggered by setting to -1 the input parameter of the ATO named IN\_EXT\_CONST\_START\_BRAKE, as in Figure 20. If the user wishes to trigger a normal scenario, in which the ATO brakes before the OBU, then the parameter shall be set to values such as 0.4, as in Figure 14. These scenarios will be discussed in the following sections, in which we describe the behaviour of the integrated model.

Figure 20 Architecture of the model that integrates Moving-block system and ATO (Part 1)

Figure 21 Architecture of the model that integrates Moving-block system and ATO (Part 2)

### 3.4.2 Integrated Model Behaviour

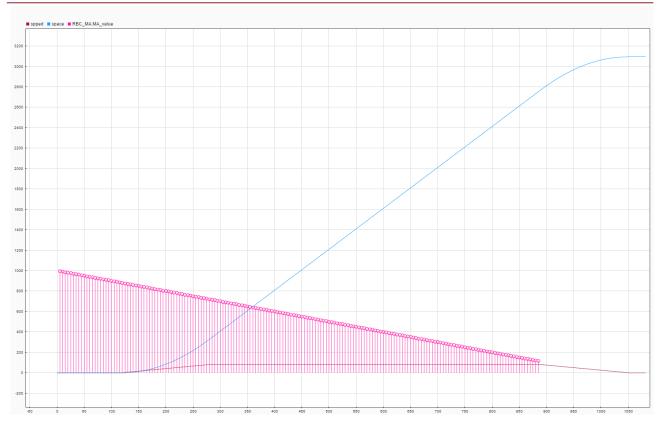

Figure 22 and Figure 23 represent the main variables of the considered integrated model, in a normal scenario. In the scenario, the ATO drives the train based on the MA produced by the RBC and forwarded by the OBU, and the OBU does not activate the emergency braking. Specifically, Figure 22 shows the value of the signal **space\_to\_EOA** as computed by the OBU, which varies in relation to the train movement and to the new MA value received from the RBC, which decreases constantly each time the OBU sends a position report. The ATO accelerates until a maximum speed value, and some space before the end of the movement authority, it starts braking. Then, when a new MA is received, the system starts moving again, after the DRIVER has allowed that, by triggering the signal **in\_DRIVE** in Figure 20.

Figure 23 focuses on the speed, accelerate and brake variables for the same scenario.

Figure 24 shows the behaviour of the system in case the ATO does not stop the train as expected, and the OBU is forced to brake. The MA values included in the messages from the RBC (pink lines) decrease until the OBU starts braking, so that the train is stopped before the end of the MA.

Figure 22 Normal behaviour of the ATO in the integrated model

Figure 23 Normal behaviour of the ATO in relation to acceleration, brake and speed

Figure 24 Case of MA violation by the ATO

# 3.5 Requirements Elicitation and Simulation with Simulink: Observations

This section is dedicated to discuss the observations through the usage of Simulink-Stateflow for early requirements elicitation and simulation in the context of ASTRail.

- Immediate visual feedback on system behaviour: when modelling through Simulink-Stateflow, the user can simulate the requirements, and have an immediate feedback of the system behaviour. This is not possible with a static diagram. Such feedback allows the user to increase their confidence on the correctness of the requirements, but also to identify incomplete requirements. A typical case of incomplete requirements occurs when one observes the simulation flipping between neighbouring states: this may occur because the conditions to remain in a certain state are not well defined. In other cases this may occur because there are variations of the input variables that are too frequent, leading to frequent switches between states. A case of incomplete, or too generic, requirements emerge when there is a the need to take some practical decision when modelling the system. Sometimes, the decisions were not necessarily guided by the requirements, which tend to abstract away from concrete behaviours. By asking the domain expert for clarifications, it was possible to further refine the requirements.

- Ease of interpretation for domain experts: in our context, the models were developed by formal methods experts, and were agreed by the domain expert. After an explanation of the principles of the Simulink-Stateflow language, and using the images of the developed Simulink-Stateflow diagrams as references, the domain expert was able to pinpoint undesired behaviour and defects in the model. At the same time, the domain expert could more easily visualise problems with the requirements that were used as a source to define the model, and take corrective actions.

- Simulation time depends on multiple factors: the model and its parameters have been set to execute

a simulation in a reasonable amount of time, and observe the train movement, acceleration and

speed with some degree of realism. The goal was to have a feeling of the overall behaviour, and not

to find the correct values of each parameter. However, the simulation time may have very relevant variations, also using the same parameters' values. These time variations are related to the processing time of the simulation, and may depend on several factors, including the size of the simulated model, and the technical capabilities of the PC. The reader will notice that in Figure 14 the parameters for the train INC CONST SPEED and INC CONST SPACE, which are used to increase speed and space of the train, are set to 0.001 and 0.0001, respectively. In Figure 21, where the integrated model is presented, these parameters are set to 0.1 and 0.01. This increase in the parameter was driven by the fact that, since the model was larger, the previous parameters would be too low to have a realistic change of the values of space and speed. Overall, when using Simulink-Stateflow for the purpose of a realistic, early simulation, these aspects need to be taken into account.

- Nondeterminism not supported: the Stateflow language does not support nondeterministic choices. This implies that the user has to define all the input and associated output, without leaving space for nondeterministic behaviour. On the one hand, this leads to a more faithful representation of the actual code that will run on the real system, which will be deterministic. On the other hand, this leaves less space to abstract away from deterministic behaviours that are not decided during the early stages of development, therefore leading to a more complex, but also more restricted model.

- Not a faithful model of reality: while the user is constrained to take some choices to let the simulation run, some of the choices taken are unavoidably a simplification of reality. For example, in Figure 11, the RBC always sends a MA with a value of 1000 meters. Although this allows the user to have an acceptable simulation as shown in Figure 18, this is not what would happen in reality, as the value of the MA may depend from the train position in relation to other trains. When integrating the movingblock system with the ATO, another problem emerged: the MA value should be reduced in a progressive manner, in order to have the ATO brake the train (we recall that the ATO mission is equivalent to the MA in this model). To address this issue and have the simulation run presented in Figure 22, the RBC needed to be modified so that it would decrease the MA value each time an MA was sent. This is of course a simplification of reality, oriented to enable a coherent collective behaviour of the different components. This is acceptable at this stage of development, as our goal is to assess the logic of interaction. However, when more detailed models are defined, these issues need to be considered, and realistic choices need to be taken.

# **Qualitative verification**

In this section we provide a description of the qualitative/functional formal specification and verification process followed, based on the process described in Sect. 2.2.2.

As said in Section 2, the initial step of the validation process has been the refinement of the initial moving block model, its extension with ATO modelling, and the animation of the composition with the Simulink-Stateflow tool. The result of this step is a stable set of natural language as reported in Annex A – System Requirements.

At this point, our interest is to define a formal model, consistent with respect to established requirements, upon which to verify the functional (behavioural) requirements of the system.

Our choice is to pass from the initial requirements and initial Simulink model towards a preliminary behavioural semi-formal description of the system based on UML statecharts.

Before tackling the issue of translating the design of the source specification language of a formal-verification tool, that could in principle be any of tools available at the state of art (e.g. CADP, ProB, SPIN), it is important to have a system design that is as clear as possible.

The Simulink model might play with some success this role, but it has three main drawbacks: the first one is that it relies on a proprietary notation which only the commercial tool is able to animate (and partly verify), the second one are the strong assumptions made in the composition of concurrent, but independent, subsystems (which are sequentially ordered and executed synchronously one step at a time), and the third one is that the Simulink model is inherently deterministic therefore specific choices need to be taken, possibly leading to over specification, to support the system simulation.

Our choice of using standard UML has been impacted by the fact that this notation has a public specification (OMG UML2.5 Specification)<sup>1</sup>, a rather clearly defined semantics when certain problematic aspects are not used, and the support of a rich set of design, transformation, animation and verification tools some of which are commercial only (e.g. IBM Rational Software Architect<sup>2</sup>, MagicDraw<sup>3</sup>, PTC Integrity Modeller<sup>4</sup>, Enterprise Architect<sup>5</sup>), while others free and open source (e.g. . OpenMBEE<sup>6</sup>), UML Designer<sup>7</sup>, UMC<sup>8</sup>, Papyrus UML<sup>9</sup>). Clearly also the standard UML choice is not immune from drawbacks, both in terms of tool support and specification language aspects, with which we will have to deal.

In Section 4.1 we will show our reference UML description of the system, while in Section 4.2 we will describe the followed approach for translation the UML description into a real formal model based on the Event B notation and in Section 4.3 the present to verification process conducted with the tool ProB while in Section 4.4 we will present some conclusions and observations.

# 4.1 The UML system description

In this section, after a brief summary of the graphical elements used in the diagrams (subsection 4.1.1), we will hint the main characteristics of our UML modelling of the Moving Block system and the ATO system (subsection 4.1.2), before presenting the detailed UML models of the OBU (subsection 4.1.3), RBC (subsection 4.1.4), and ATO (subsection 4.1.5) system components.

#### 4.1.1 Briefs on the used UML statecharts notation

In the following sections we will present a graphical representation of the OBU, RBC, ATO components of the system. Those graphical representations will make essentially use of the following symbols:

denoting the initial state of a composite sequential state.

<sup>&</sup>lt;sup>1</sup> https://www.omg.org/spec/UML/2.5.1/PDF

<sup>&</sup>lt;sup>2</sup> https://www.ibm.com/developerworks/downloads/r/architect/index.html

<sup>&</sup>lt;sup>3</sup> <a href="https://www.nomagic.com/products/magicdraw">https://www.nomagic.com/products/magicdraw</a>

<sup>4</sup> www.ptc.com

<sup>&</sup>lt;sup>5</sup> https://sparxsystems.com/products/ea

<sup>&</sup>lt;sup>6</sup> http://www.openmbee.org

<sup>&</sup>lt;sup>7</sup> http://www.umldesigner.org/

<sup>8</sup> https://fmt.isti.cnr.it/umc

<sup>9 &</sup>lt;u>https://www.eclipse.org/papyrus/</u>

denoting the exit point from a composite state (or submachine)

denoting a simple state of the model

denoting a composite state of the system separately expanded (i.e. a submachine).

o1 startcycle. tick/ Timer.ok OBU\_500MS BEGIN\_OBU\_CYCLE

denoting the information associated to a transition between states, where in particular:

- The **red** identifier represents a unique label associated to the edge (used for the ProB translations)

- The trigger part (on the left side of "/") denotes the event triggering the transition (highlighted in italic) and possible a guard condition.

In particular:

The trigger "tick" denotes a clock event signalling the passing of 500 ms.

The trigger "istep" denotes the execution of an internal step, not trigger by any external event.

- Transitions without trigger (with trigger represented by "-") denote "UML completion transitions" and, as required by the UML semantics, have a higher priority w.r.t all other triggered transitions.

- The actions part (on the right side of "/") denotes the sequence of actions performed when the transition is fired.

- The action of sending a signal to another active component is highlighted using a **bold** case.

- The GREEN IDENTIFIERS are used to denote the abstract events corresponding to the triggering of the transition (useful for mapping the properties to be verified to the actual system evolutions).

Notice that the red and green parts of this information are not part of the UML specification and have just an informative role (with no semantic effects).

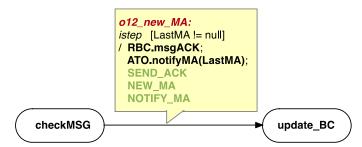

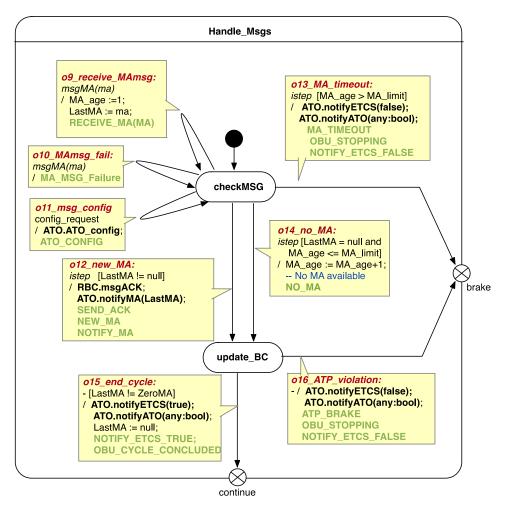

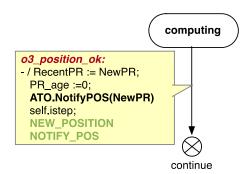

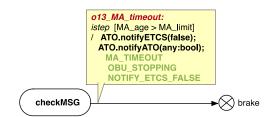

For example the diagram fragment illustrated in Figure 25 A statechart diagram fragment describes that when the state checkMSG is active, when the signal istep can be dispatched from the event pool, and when the guard LastMA != null is true, then the signal istep can be removed from the pool and the object can move into the update BC state, after sending to the RBC object the msqACK signal. That system evolution, to which has been given the name o12 new MA corresponds the to tree abstract events (maybe mentioned in the requirements) i.e. the fact of having received a new MA (NEW MA), the fact of having sent the corresponding ACK (SEND ACK), and the sending of the MA data to the ATO (NOTIFY MA).

Figure 25 A statechart diagram fragment

We refer to the OMG UML2.5 Specification - Section 14 State Machines - for a more detailed and complete description of the semantics of UML statecharts and of the statecharts graphical notation.

#### Some differences w.r.t Simulink/Stateflow modelling 4.1.2

The semi-formal specification language used for this step, and the necessary choices to be performed in the modelling, inevitably introduce a specific language/tool flavour to the result. This is the reason for which the formal model resulting from this step is somewhat different from the Simulink model already developed during the requirements elicitation phase.

Some examples between the two semi-formal methodologies of system design are the following:

- The Simulink model relies on internal timers to represent time-related aspects of the model, while our UML models relies on explicit "tick" signals arriving from the environment as a way to represent

- In a Stateflow chart the transitions exiting from a state are numbered and their number represents the order in which they should evaluated for execution, while in UML there is no such numbering and any priority among the exiting transitions should be explicitly modelled by the conditions appearing in

- In Stateflow a transition which has source in a composite state has a higher priority than any transition nested inside the composite state itself, while in UML the converse applies.

- When a Stateflow model includes different statecharts representing concurrent entities, the possible evolutions of the system are obtained by letting each component to advance one step, in a statically fixed order. The UML definition does not actually specify the behaviour of a system composed by several independent state machines. Only in the case of concurrent regions of the same parallel state the UML definition specifies that all the fireable parallel transitions should be fired in the same run-to-completion step in an unspecified order. In our UML model of the system we suppose that the state machines corresponding to the various system components (OBU, RBC, ATO) can evolve independently and asynchronously, being coordinated only through their exchanges of messages, or explicit - time modelling - "tick" signals. We moreover suppose that the event pools associated to each object are plain FIFO queues.

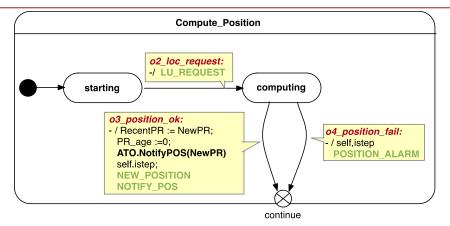

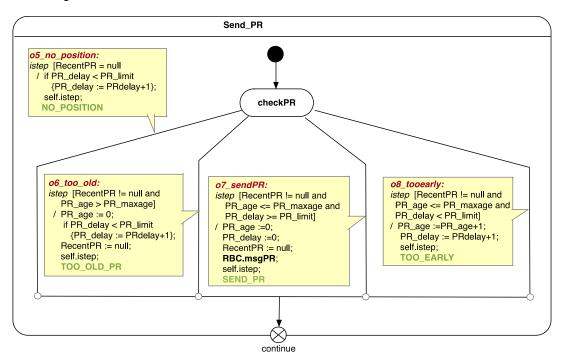

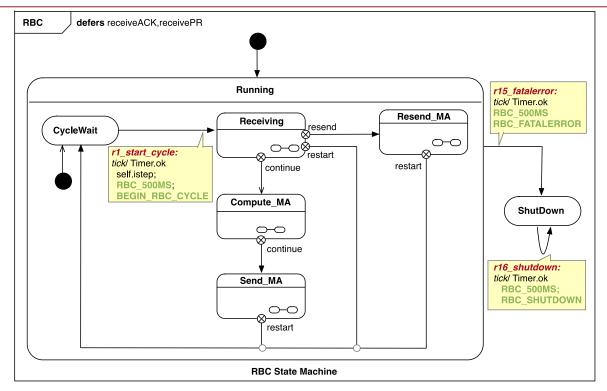

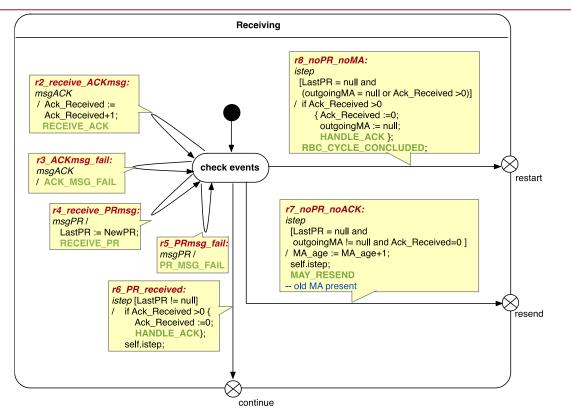

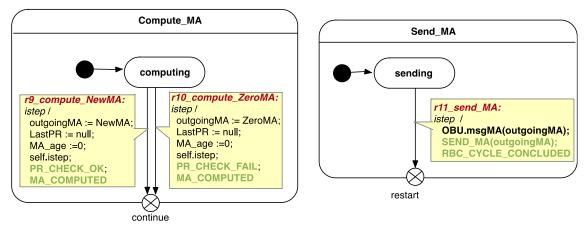

#### Introduction to the Moving Block and ATO UML modelling 4.1.3

The three main components of our system are the OBU, the RBC, and the ATO. In our case, we abstract from a separate modelling of the LU as an independent entity, and we consider it just an internal sub-activity of the OBU. When not necessary for the verification of the system requirements, the interactions of our main components with other external components of the system are abstracted without explicitly modelling the details of them. For example, when the OBU commands an emergency braking because of an ATP violation, we model this fact as an occurring abstract event ATP\_BRAKE (the abstract events occurring as logical effect of a transition are highlighted in green) without actually modelling the sending of signal from the OBU the train component.

Following the same abstraction principle, we do not model the precise data and messages being exchanged between OBU and the RBC (or OBU and ATO), like the actual train position data or the actual structure of the movement authority data. From our abstract point of view, it is sufficient to know that a new movement authority has been sent by the RBC and received by the OBU, or that a new Position Report has been sent by the OBU and received by the RBC.

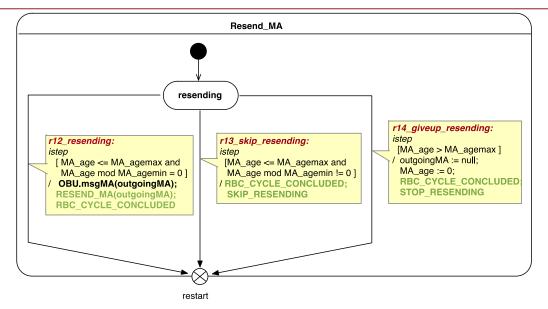

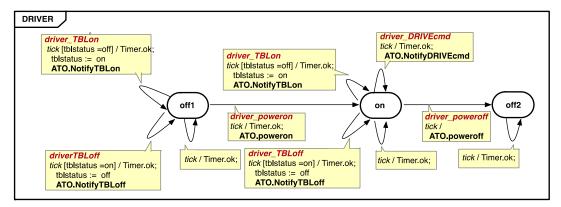

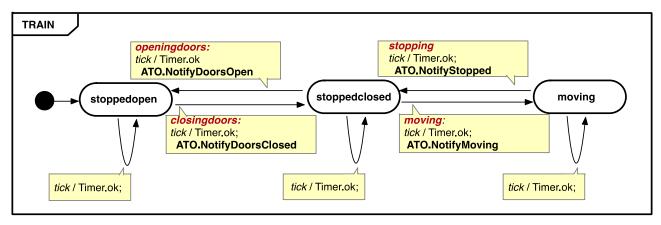

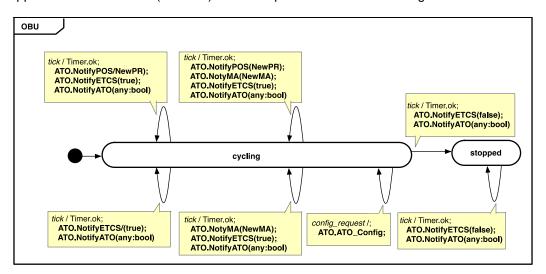

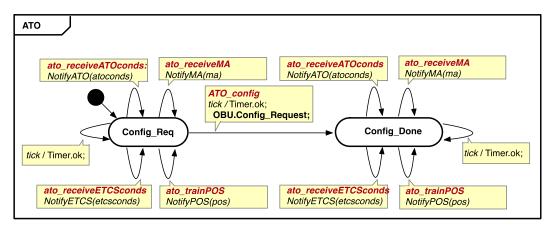

In the design of ATO we abstract from the actual values of the current movement authority, the current train position and speed, and therefore from the actual acceleration deceleration commands used to drive the train according to some driving strategy when in the Engaged or Disengaged states. Our model also does not take into consideration all the driving aspects related to the interactions with the Trackside component related, e.g. to the details of the possible train mission data.