# Efficient static analysis and verification of featured transition systems

Maurice H. ter Beek<sup>1</sup> • Ferruccio Damiani<sup>2</sup> • Michael Lienhardt<sup>3</sup> • Franco Mazzanti<sup>1</sup> • Luca Paolini<sup>2</sup> •

Accepted: 17 December 2020Published online: 23 October 2021 © The Author(s) 2021

#### **Abstract**

A Featured Transition System (FTS) models the behaviour of all products of a Software Product Line (SPL) in a single compact structure, by associating action-labelled transitions with features that condition their presence in product behaviour. It may however be the case that the resulting featured transitions of an FTS cannot be executed in any product (so called dead transitions) or, on the contrary, can be executed in all products (so called false optional transitions). Moreover, an FTS may contain states from which a transition can be executed only in some products (so called hidden deadlock states). It is useful to detect such ambiguities and signal them to the modeller, because dead transitions indicate an anomaly in the FTS that must be corrected, false optional transitions indicate a redundancy that may be removed, and hidden deadlocks should be made explicit in the FTS to improve the understanding of the model and to enable efficient verification—if the deadlocks in the products should not be remedied in the first place. We provide an algorithm to analyse an FTS for ambiguities and a means to transform an ambiguous FTS into an unambiguous one. The scope is twofold: an ambiguous model is typically undesired as it gives an unclear idea of the SPL and, moreover, an unambiguous FTS can efficiently be model checked. We empirically show the suitability of the algorithm by applying it to a number of benchmark SPL examples from the literature, and we show how this facilitates a kind of family-based model checking of a wide range of properties on FTSs.

**Keywords** Software product lines · Formal specification · Behavioural model · Featured transition systems · Static analysis · Formal verification

#### 1 Introduction

Software Product Line Engineering (SPLE) advocates the reuse of components (systems as well as software) throughout all phases of product development. Following this paradigm,

Communicated by: Laurence Duchien, Thomas Thüm and Paul Grünbacher

This article belongs to the Topical Collection: Configurable Systems

Ferruccio Damiani

ferruccio damiani@unito it

Extended author information available on the last page of the article.

10 Page 2 of 43 Empir Software Eng (2022) 27:10

businesses today no longer develop single products, but families or product lines of closely-related, customisable products. Upon identifying the relevant features of the product domain, to exploit their commonality and variability, a feature diagram or feature model defines those combinations of features that constitute valid product configurations (Apel et al. 2013). The automated analysis of such variability models has a 30-year history (Benavides et al. 2010; Thüm et al. 2014). Think, e.g., of the detection of anomalies like so called dead or false optional features. Behavioural models with variability, on the other hand, have a shorter history (Fischbein et al. 2006; Fantechi and Gnesi 2007, 2008; Larsen et al. 2007; Gruler et al. 2008; Asirelli et al. 2009; Lauenroth et al. 2009) and they have received considerable attention only during the last decade, following the seminal paper by Classen et al. (2010). SPLs often concern massively (re)used critical software (e.g., in smartphones and the automotive industry), thus it is important to demonstrate their correct behaviour next to their correct configuration.

A Featured Transition System (FTS) is a formal model with variability for capturing the behaviour of all products of an SPL in one compact model (Classen et al. 2013; Cordy et al. 2019); its action-labelled transitions are associated with features that condition their presence in product behaviour. Proving correctness of such models through model checking or testing is challenging. Ideally, the compact structure of the FTS is exploited to reason on the whole SPL at once. Such an *all-in-one* technique, according to which the behaviour of all products is examined only once simultaneously, is called family-based analysis in contrast to a brute force enumerative product-based analysis, according to which the behaviour of every product is examined individually, *one-by-one* (Thüm et al. 2014). Over the past decade, FTSs have shown to be amenable to family-based testing and model-checking (Kim et al. 2011; Classen et al. 2012, 2013, 2014; Cordy et al. 2013a; Devroey et al. 2014b, 2016b; ter Beek et al. 2015b, 2017, 2020b; Dimovski et al. 2017; Dimovski and Wąsowski 2017; Dimovski 2020).

In ter Beek et al. (2019a), we tackled the automated static analysis of FTSs. We defined the following three ambiguities for an FTS: a *dead transition* (i.e., a featured transition that is unreachable, and thus cannot be executed, in any product); a *false optional transition* (i.e., a featured transition that can be executed in all products in which its source state is reachable); and a *hidden deadlock state* (i.e., a state from which a transition can be executed only in some products). We developed an algorithm to detect ambiguities in FTSs (and a means to resolve them), mimicking the well-established anomaly detection for feature models, with a proof of its correctness. The motivations we presented in ter Beek et al. (2019a) were twofold: an ambiguous FTS is often undesired, since it gives an unclear idea of the SPL behaviour, and an unambiguous FTS paves the way for an efficient kind of family-based model checking. We illustrated the latter on a few examples from the literature.

This paper extends ter Beek et al. (2019a) in the following ways.

- 1. We introduce an engineering methodology aimed towards providing feedback to SPL modellers to possibly improve their FTS models and, subsequently, a strategy which offers a number of verification options (cf. Fig. 4). A dead transition in an FTS indicates a modelling error that must be corrected. A false optional transition indicates a redundancy that may be intentional, but resolving it allows for more efficient verification options. A hidden deadlock should be made explicit in the model to improve understanding and to enable an efficient kind of family-based verification—if the deadlocks in the products that are the cause should not be remedied in the first place.

- Driven by the need to improve the practical applicability of our automated static analysis for behavioural ambiguity detection in FTSs, we present a new algorithm (more

Empir Software Eng (2022) 27:10 Page 3 of 43 10

efficient than that presented in ter Beek et al. (2019a)) for detecting ambiguities in FTSs by reducing the analysis to SAT solving. In addition, we prove its correctness.

- 3. To demonstrate the improved practical applicability, we apply our algorithm to a larger set of benchmark SPL examples than in ter Beek et al. (2019a), including the FTS of the complete mine pump model of Classen (2010, 2011) and that of the Claroline SPL of Devroey et al. (2014a) with over 10,000 transitions, both of which are not tractable with the algorithm presented in ter Beek et al. (2019a). We empirically show the suitability of the new algorithm by means of a clear runtime speedup.

- 4. We capitalise on the promise of an efficient kind of family-based model checking by demonstrating how properties specified in either the well-known Linear-time Temporal Logic (LTL) or in v-ACTLive□, a rich action-based and variability-aware fragment of the well-known branching-time Computation Tree Logic (CTL), can be verified (with a linear complexity) directly on an unambiguous FTS (ignoring its feature expressions) such that validity is preserved in all LTSs modelling product behaviour. The preservation of valid v-ACTLive□ properties was anticipated in ter Beek et al. (2019a), while the preservation of valid LTL properties was not observed before. These results imply the addition of two efficient verification options to the above mentioned strategy provided to SPL modellers (cf. Fig. 4).

**Outline** After mentioning some related work in Section 2 and providing some background in Section 3, we provide our engineering methodology in Section 4 by defining ambiguities in FTSs and providing a means to resolve them. In Section 5, we present the new static analysis algorithm to detect ambiguities in FTSs, based on SAT solving, and prove its correctness. In Section 6, we empirically show the suitability of the new algorithm by applying it to a number of exemplary FTSs from the literature. In Section 7, we show the feasibility of an efficient kind of family-based model checking of FTSs made possible by the static analysis algorithm. Finally, we conclude the paper in Section 8.

#### 2 Related work

Static analysis of FTSs mimics the automated analysis of feature models by defining behavioural counterparts of dead and false optional features (Benavides et al. 2010; Thüm et al. 2014). It is related to static (program) analysis (Nielson et al. 2005; Chess and West 2007), which includes the detection of bugs in the code (like using a variable before its initialisation) but also the identification of code that is redundant or unreachable.

In Kim et al. (2011), conventional static analysis techniques are applied to SPLs that are represented in the form of object-oriented programs with feature modules. The aim is to find irrelevant features for a specific test in order to use this information to reduce the effort in testing an SPL by limiting the number of SPL programs to examine to those with relevant features. In Bodden et al. (2013), several well-known static analysis techniques are lifted to Java-based SPLs without the exponential blowup caused by generating and analysing all products individually. This is achieved by converting such analyses to feature-sensitive analyses that operate on the entire SPL code in one single pass. Basically, if the original analysis reports that a data-flow property holds at a given program statement, then the lifted analysis reports a feature constraint (a logical expression over the set of features) under which that property holds at the given statement.

In Kästner and Apel (2008), static type checking is extended from single programs to an entire SPL (program family) by extending the type system of a subset of Java with feature

10 Page 4 of 43 Empir Software Eng (2022) 27:10

annotations. This guarantees that whenever the SPL is well-typed, then all possible program variants are well-typed as well, without the need to generate and compile them first.

In Delaware et al. (2009), type-checking for product lines is mechanised and soundness of a constraint-based type system for Lightweight Feature Java (LFJ), an extension of Lightweight Java with support for features, is proved using a full formalisation of LFJ in the Coq proof assistant (Bertot and Castéran 2004).

An encompassing overview of analysis strategies for SPLs, including type checking, static analysis, model checking, and theorem proving, can be found in Thüm et al. (2014) and a recent empirical study on applying variability-aware static analysis techniques to real-world configurable systems is presented in von Rhein et al. (2018).

Family-based model checking of behavioural SPL models provides a means to simultaneously verify multiple behavioural product models in a single run. Properties can be verified with dedicated SPL model-checking tools such as SNIP (Classen et al. 2012, 2013, ProVe-Lines (Cordy et al. 2013a), VMC (ter Beek et al. 2012, 2016a; ter Beek and Mazzanti 2014), fNuSMV (Classen et al. 2014; Dimovski et al. 2019), ProFeat (Chrszon et al. 2018) (for probabilistic model checking), or QFLan (ter Beek et al. 2020a; Vandin et al. 2018) (for statistical model checking), or—through suitable abstractions or encodings—with well-known classical model checkers like SPIN (Dimovski et al. 2015, 2017; Dimovski and Wąsowski 2017), PRISM (Dubslaff et al. 2015) (for probabilistic model checking), Maude (Lochau et al. 2016), mCRL2 (ter Beek et al. 2017, 2020b), or NuSMV (Dimovski 2020).

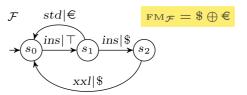

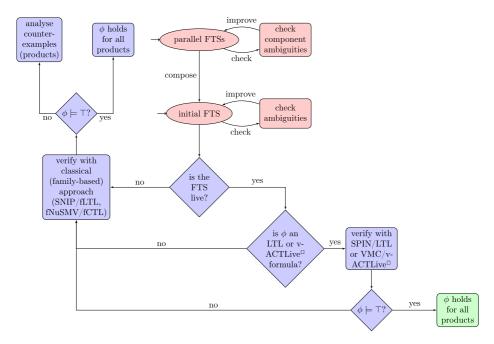

In this paper, we introduce an engineering methodology that enables a kind of family-based model checking for FTSs, according to a strategy that is sketched in Fig. 4 (the part that is not in red). This figure will be discussed in more detail in Sections 4 and 7. The strategy that is sketched is as follows. If (i) the FTS is live, which is the case whenever it has no hidden deadlocks (so, unambiguous FTSs are live), and (ii) the property  $\phi$  to be verified is specified in either LTL or v-ACTLive , then  $\phi$  can be verified directly on the FTS (by ignoring its feature expressions) and if (iii)  $\phi$  holds, this validity is preserved in all LTSs modelling product behaviour, i.e.  $\phi$  holds for all products. If any of these three conditions does not hold, the property needs to be verified with classical (family-based) approaches, such as the ones mentioned above.

The verification methodology depicted in Fig. 4 thus indicates specific cases in which verification of live FTSs reduces to verification of corresponding MTSs and LTSs (which, as we will see, can be obtained straightforwardly by ignoring the feature expressions, and distinguishing necessary and optional transitions in case of MTSs) with a linear complexity.

However, if either (i) the property to be verified is not a v-ACTLive<sup>□</sup> or LTL formula, or (ii) the result of the verification is false, then the formula needs to be verified with classical family-based model checking or by means of product-based model checking, with an exponential complexity (Classen et al. 2013, 2014).

# 3 Background

In this section, we provide some background needed for the sequel. Labelled Transition Systems (LTSs) are the underlying behavioural structure of FTSs.

**Definition 1** (LTS) A *Labelled Transition System* (LTS) is a quadruple  $\mathcal{L} = (S, \Sigma, s_0, \delta)$ , where S is a finite (non-empty) set of states,  $\Sigma$  is a set of actions,  $s_0 \in S$  is an initial state, and  $\delta \subseteq S \times \Sigma \times S$  is a transition relation.

Empir Software Eng (2022) 27:10 Page 5 of 43 10

We call  $(s, a, s') \in \delta$  an a-(labelled) transition (from source state s to target state s') and we may also write it as  $\xrightarrow{a} s'$ .

We recall classical notions for LTSs that will be used throughout the paper.

**Definition 2** (reachability) Let  $\mathcal{L} = (S, \Sigma, s_0, \delta)$  be an LTS.

A sequence  $p = s_0 t_1 s_1 t_2 s_2 \cdots$  is a *path* of  $\mathcal{L}$  if  $t_i = (s_{i-1}, a_i, s_i) \in \delta$  for all i > 0; p is said to *visit* states  $s_0, s_1, \ldots$  and transitions  $t_1, t_2, \ldots$  and we denote its ith state by p(i) and its ith transition by  $p\{i\}$ .

A state  $s \in S$  is *reachable* (via p) in  $\mathcal{L}$  if there exists a path p that visits it, i.e., p(i) = s for some  $i \geq 0$ ; s is a *deadlock* if it has no outgoing transitions, i.e.,  $\nexists (s, a, s') \in \delta$ , for all  $a \in \Sigma$  and  $s' \in S$ .

A transition  $t = (s, a, s') \in \delta$  is *reachable* (via p) in  $\mathcal{L}$  if there exists a path p that visits it, i.e.,  $p\{i\} = t$ , for some i > 0.

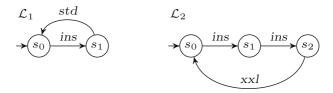

Example 1 In Fig. 1, we depict the LTSs  $\mathcal{L}_1$  and  $\mathcal{L}_2$ , modelling the behaviour of two different coffee machines, adapted from ter Beek et al. (2017, 2019a). Each LTS has actions to insert coins (*ins*) and to pour either standard (*std*) or extra large (*xxI*) coffee upon the insertion of one or two coins, respectively. Clearly all states are reachable and there are no deadlocks.

FTSs were introduced in Classen et al. (2010) to concisely model the behaviour of all the products of an SPL, modelled as LTSs, in one transition system by annotating transitions with conditions expressing their presence in (product) LTSs. Let  $\mathbb{B} = \{\top, \bot\}$  denote the Boolean constants true  $(\top)$  and false  $(\bot)$ , and let  $\mathbb{B}(F)$  denote the set of propositional formulas over a set of features F (i.e., using features as propositional variables). We do not formalise a language for propositional formulas in order to allow the inclusion of all possible propositional connectives but, in particular, we include the constants from  $\mathbb{B}$ . The elements of  $\mathbb{B}(F)$  are also called *feature expressions*. An FTS is an LTS equipped with a feature model and a function that labels each transition with a feature expression. In the following definition, the feature model is represented by the set of its (product) configurations, where each configuration is represented by a Boolean assignment to the features (i.e., selected =  $\top$  and unselected =  $\bot$ ).

**Definition 3** (FTS) A *Featured Transition System* (FTS) is a sextuple  $\mathcal{F} = (S, \Sigma, s_0, \delta, F, \Lambda)$ , where S is a finite (non-empty) set of states,  $\Sigma$  is a set of actions,  $s_0 \in S$  is the initial state,  $\delta \subseteq S \times \Sigma \times \mathbb{B}(F) \times S$  is a transition relation, F is a set of features, and  $\Lambda \subseteq \{\lambda : F \to \mathbb{B}\}$  is a set of *(product) configurations.*

**Fig. 1** LTSs  $\mathcal{L}_1$  and  $\mathcal{L}_2$  modelling coffee machines

10 Page 6 of 43 Empir Software Eng (2022) 27:10

Given a feature expression  $\phi \in \mathbb{B}(F)$ , we call  $(s, a, \phi, s') \in \delta$  featured transition (labelled with a and limited to configurations satisfying  $\phi$ ) and  $(s, a, \top, s') \in \delta$  must transition. We may write featured transitions as  $s \xrightarrow{a \mid \phi} s'$ .

The notions from Definition 2 (path, reachability, deadlock) are carried over to FTSs by ignoring the feature expressions.

A configuration  $\lambda \in \Lambda$  satisfies a feature expression  $\phi \in \mathbb{B}(F)$ , denoted by  $\lambda \models \phi$ , whenever  $\phi$  is valid in the interpretation  $\lambda$ , i.e., the result of substituting the value of the features occurring as variables in  $\phi$  according to  $\lambda$  is  $\top$ . Thus, by definition,  $\lambda \models \top$ .

Without loss of generality, in the sequel we only consider FTSs that do not contain two featured transitions  $q \xrightarrow{a \mid \phi} q'$  and  $q \xrightarrow{a \mid \phi'} q'$  such that  $\phi \neq \phi'$ . Any FTS that does not satisfy this criterion can be transformed into one that does by replacing the two transitions with one featured transition  $q \xrightarrow{a \mid \phi \lor \phi'} q'$ .

## **Definition 4** (product) Let $\mathcal{F} = (S, \Sigma, s_0, \delta, F, \Lambda)$ be an FTS.

The LTS specified by a particular configuration  $\lambda \in \Lambda$ , denoted by  $\mathcal{F}|_{\lambda}$ , is called a *product* of  $\mathcal{F}$ . It is obtained from  $\mathcal{F}$  by first removing all featured transitions whose feature expressions are not satisfied by  $\lambda$  (resulting in the LTS  $(S, \Sigma, s_0, \delta')$ , with  $\delta' = \{(s, a, s') \mid (s, a, \phi, s') \in \delta \text{ and } \lambda \models \phi\}$ ), and then removing all unreachable states and their outgoing transitions.

Given a featured transition  $(s, a, \phi, s') \in \delta$ , we call  $(s, a, s') \in \delta'$  its *corresponding (LTS) transition*. The set of products of  $\mathcal{F}$  is denoted by lts $(\mathcal{F})$ .

Note that, by construction: (i) each product does not contain unreachable states or transitions, (ii) each must transition of the FTS has a corresponding transition in the products in which it is reachable, (iii) each product does not contain states or actions that were not originally present in the FTS, and (iv) each featured transition has a unique corresponding LTS transition when its source state is reachable.

The *feature model expression* of  $\mathcal{F}$ , denoted by  $FM_{\mathcal{F}}$ , is a feature expression that represents  $\Lambda$  (like, e.g., the formula in conjunctive normal form  $\bigvee_{\lambda \in \Lambda} (\bigwedge_{f \in F} (\{f \mid \lambda(f) = \top\}) \cup \{\neg f \mid \lambda(f) = \bot\})$ ). Thus, for all  $\lambda : F \to \mathbb{B}$  it holds that  $\lambda \models FM_{\mathcal{F}}$  if and only if  $\lambda \in \Lambda$ . We may write FM instead of  $FM_{\mathcal{F}}$  if no confusion can arise.

*Example 2* In Fig. 2, we depict an FTS  $\mathcal{F}$  modelling the behaviour of the two coffee machines from Example 1 as a product line of coffee machines, adapted from ter Beek et al. (2017, 2019a). Imagine that extra large coffee is exclusively available for the American market, while standard coffee is exclusively available for the European market. To this aim,  $\mathcal{F}$  has transitions labelled with features \$ and €, representing products for either the American or the European market, respectively, and a must transition that must be present in every product. Its feature model, depicted in Fig. 3(left), can be represented by the feature

Fig. 2 FTS  $\mathcal{F}$  modelling a product line of coffee machines

Empir Software Eng (2022) 27:10 Page 7 of 43 10

**Fig. 3** Feature models of product line of coffee machines (left), with a dead feature (middle), and with a false optional feature (right)

expression  $FM_{\mathcal{F}} = \$ \oplus \mbox{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextchar[{\@ifnextc$

Parallel composition of FTSs is equal to the classical parallel composition of LTSs modulo projection (Classen 2011, 2013). Intuitively, parallel composition partially interleaves the transitions of the LTSs, permitting asynchronous execution of their actions, except for those with shared actions, which are synchronised, thus only permitting execution of their actions at the same time. In case of FTSs, the feature expressions of synchronised transitions are conjuncted, while each interleaved transition simply maintains its feature expression (Classen 2011; Classen et al. 2013).

## 4 Ambiguities in FTSs

When applying automated analysis of feature models, the better known analysis operations that are typically being performed concern the detection of anomalies (cf., e.g., Benavides et al. 2010; Thüm et al. 2014). These anomalies reflect ambiguous or even contradictory information. Examples include so-called dead and false optional features. A feature is *dead* if it is not contained in any product configuration of the FTS, whereas it is *false optional* if it is contained in all product configurations of the FTS even though it is not a designated mandatory feature. Such anomalies are typically due to an incorrect use of cross-tree constraints. Consider the feature models depicted in Fig. 3. The one on the left corresponds to the feature model expression  $\$ \oplus \texttt{C}$  from Example 2 and it has neither dead nor false optional features. The one in the middle corresponds to the feature model expression  $\$ \land (\$ \uparrow \texttt{C})$ , where  $\uparrow$  is the negation of conjunction (a.k.a. *not and*), and it has a dead feature C, indicated in red, because this optional feature is excluded by the mandatory feature \$ and thus never present. The feature model on the right, finally, corresponds to the feature model expression  $\$ \land (\$ \rightarrow \texttt{C})$ , meaning that C is false optional, indicated in red, because it is required by the mandatory feature \$ and as such always present.

In this section, we formalise equivalent notions in a behavioural setting, by adapting the above notions to (featured) transitions of an FTS (Section 4.1). Furthermore, we define ambiguous FTSs and we show how to transform any ambiguous FTS into an unambiguous one (Section 4.2). This constitutes our envisioned engineering methodology, which is

$<sup>^1</sup>$ We foresee an optimisation of conjuncted feature expressions to foster useful output (e.g., the synchronisation of two must transitions could lead to a conjuncted feature expression  $\top \land \top$ , which would technically not be a must transition according to Definition 3 and could thus be detected as a false optional transition, as we will see in Definition 6(ii).

10 Page 8 of 43 Empir Software Eng (2022) 27:10

sketched in Fig. 4 (the top-right red part) together with a number of verification options (the part of Fig. 4 that is not red) organised in a strategy that was briefly outlined in Section 2 and which will be discussed in more detail in Section 7. This engineering methodology improves the clarity of behavioural SPL models, which is one of the contributions of this paper.

## 4.1 Behavioural ambiguities

Recall from Definition 4 that all states of a (product) LTS of an FTS are reachable from the initial state.

**Definition 5** (dead transition) We say that a transition (of an FTS) is *dead* to mean that in all the FTS's products the corresponding (LTS) transition is not reachable.

Clearly, since an FTS is intended to compactly represent the behaviour of all products of a product line, a dead transition in an FTS indicates a modelling error that must be signalled to the modeller so it can be corrected. Such correction can mean removing the transition or changing its feature expression.

**Definition 6** (false optional transition) We say that a transition (of an FTS) is *false optional* to mean that: (i) it is not dead, (ii) it is not annotated with the feature expression  $\top$ , and (iii) its corresponding (LTS) transition is present in all the FTS's products in which its source state is present.

Definition 6 is a slightly revised version of that of ter Beek et al. (2019a, Def. 3.2), in which condition (i) was not explicitly required. Note that condition (iii) does not imply

Fig. 4 Engineering methodology (top-right red part) and verification options (not in red)

Empir Software Eng (2022) 27:10 Page 9 of 43 10

condition (i). In fact, condition (i) requires the source state of the considered transition to be present (i.e., reachable) in at least one product of the FTS, which is not guaranteed by condition (iii).

A false optional transition in an FTS indicates a redundancy, in the sense that the associated feature expression can be replaced by  $\top$  without changing the behaviour of any of the products of the product line. This redundancy may be intentional syntactic sugar, to underline the fact that the considered transition is part of the behaviour of those product configurations that satisfy the feature expression, but otherwise it may be useful for the modeller to know. Moreover, as we will see in Section 7, substitution of the feature expression with  $\top$  allows for more efficient verification because it results in one more must transition, and thus one less feature expression to be evaluated.

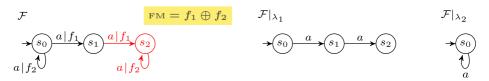

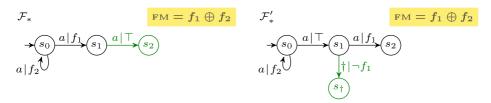

Example 3 In Fig. 5(left), we depict an FTS  $\mathcal{F}$  with features  $f_1$  and  $f_2$  and feature model FM =  $f_1 \oplus f_2$ . The LTSs  $\mathcal{F}|_{\lambda_1}$  and  $\mathcal{F}|_{\lambda_2}$ , depicted in Fig. 5(middle and right), model the behaviour of its two valid product configurations:  $\lambda_1 = \{f_1\}$  and  $\lambda_2 = \{f_2\}$ . We immediately see that transition  $s_2 \xrightarrow{a \mid f_2} s_2$  is dead and transition  $s_1 \xrightarrow{a \mid f_1} s_2$  is false optional.

An important safety property of systems concerns *deadlock freedom*, i.e., the system should not reach a state in which no further action is possible, thus guaranteeing progress or liveness (Alpern and Schneider 1985; Manna and Pnueli 1995). In case of configurable systems (like FTSs) this notion can be extended to guaranteeing liveness for each product variant (LTS).

In order to express this notion in the context of FTSs, we introduce the following definition (recall from Section 3 that a state of an FTS is said to be a deadlock if it has no outgoing transitions).

**Definition 7** (hidden deadlock state) We say that a state (of an FTS) is a *hidden deadlock* to mean that: (i) it is not a deadlock in the FTS, whereas (ii) it is a deadlock in at least one of the FTS's products (LTSs).

Note that, because of condition (ii) in Definition 7, hidden deadlock states of an FTS are present in one or more of its (product) LTSs.

A hidden deadlock in the FTS should definitely be signalled to the modeller, so it can be checked whether the deadlocks in the LTSs should be remedied. If they should not, i.e., if the deadlocks in the LTSs are intended or unavoidable, then this should be made explicit in the FTS to improve understanding. Moreover, as we will see below, this enables a kind of family-based verification.

**Definition 8** (ambiguous FTS) We say that an FTS is *ambiguous* to mean that: (i) at least one of its states is a hidden deadlock, or (ii) at least one of its transitions is dead or false optional.

**Fig. 5** FTS  $\mathcal{F}$  and its product LTSs  $\mathcal{F}|_{\lambda_1}$  and  $\mathcal{F}|_{\lambda_2}$

10 Page 10 of 43 Empir Software Eng (2022) 27:10

Example 4 It is easy to see that state  $^{52}$  of the FTS  $\mathcal{F}$  depicted in Fig. 5(left) is a hidden deadlock state, because  $^{52}$  is a deadlock in the LTS  $\mathcal{F}|_{\lambda_1}$ . Indeed,  $\mathcal{F}$  is an ambiguous FTS (cf. also Example 3).

Now consider the ambiguous FTS  $\mathcal{F}'$  depicted in Fig. 6(left) with features  $f_1$  and  $f_2$  and feature model FM =  $f_1 \oplus f_2$ .

The LTSs  $\mathcal{F}'|_{\lambda_1}$  and  $\mathcal{F}'|_{\lambda_2}$ , depicted in Fig. 6(middle and right), model the behaviour of its two valid product configurations:  $\lambda_1 = \{f_1\}$  and  $\lambda_2 = \{f_2\}$ . Similar to Example 3, transition  $s_2 \xrightarrow{a \mid f_2} s_2$  is dead. However, transition  $s_1 \xrightarrow{a \mid f_1} s_2$  is no longer false optional, since it is indeed not present in  $\mathcal{F}'|_{\lambda_2}$  even though its source state  $s_1$  is reachable in that LTS. Moreover, not only state  $s_2$  is a hidden deadlock (for the same reason as above) but so is state  $s_1$ , since it is a deadlock in  $\mathcal{F}'|_{\lambda_2}$ . Hence also  $\mathcal{F}'$  is ambiguous.

In Definition 8, an FTS is said to be ambiguous if it has a hidden deadlock state or a dead or false optional transition. We can imagine further ambiguities. For instance, consider for a moment an FTS with the two 'nearly' duplicate transitions  $q \xrightarrow{a \mid f} q'$  and  $q \xrightarrow{a \mid f \land g} q'$  (such FTSs are generally not considered in this paper, cf. Section 3). Then the second transition is redundant, since the validity of its feature expression implies that of the first transition, meaning that the second transition adds no behaviour. This clearly represents a kind of ambiguity, since looking at that second transition in isolation it would seem that execution of a requires the presence of features f and g, while actually the presence of f suffices.

Clearly, it is unlikely that systems over a certain size are modelled as single monolithic FTSs. Typically, (large) systems are designed in a modular way, as a composition of (smaller) components. We will see examples of such systems in Section 6. Our engineering methodology goes into that direction. The feedback that our analysis provides to the modellers offers them a means to revise their (small) models before composing these models to form (larger) systems.

## 4.2 Resolving ambiguities

The initial part of our engineering methodology (i.e., the top-right red part of Fig. 4) concerns checking for ambiguities. Next to providing feedback to the modeller, it is important to know how to resolve ambiguities in an FTS. A dead transition could simply be removed, but this might not be the right thing to do, since the modeller may simply have made a mistake in the behavioural model or in the feature model. Likewise for a false optional transition, which however could also be intentional, to make explicit that the (corresponding) transition is part of the behaviour of those product configurations that satisfy the associated feature expression. Finally, a hidden deadlock should either be made explicit in the FTS, which can be done by adding a deadlock state to the FTS, or the deadlocks in the LTSs should be remedied—again by changing the behavioural model or the feature model.

**Fig. 6** FTS  $\mathcal{F}'$  and its product LTSs  $\mathcal{F}'|_{\lambda_1}$  and  $\mathcal{F}'|_{\lambda_2}$

Empir Software Eng (2022) 27:10 Page 11 of 43 10

Fig. 7 Unambiguous FTSs obtained from the FTSs of Figs. 5 and 6

Hence, based on the detailed feedback obtained, the modeller can iteratively improve and check the FTS until the FTS is either unambiguous or ambiguous, but such that it is the FTS as intended by the modeller.

In the latter case, according to the above recipes, any ambiguous FTS can be straightforwardly turned into an unambiguous FTS by the following transformation:

- 1. remove the dead transitions;

- 2. turn the false optional transitions into must transitions; and

- 3. make explicit the hidden deadlocks by adding to the set of states S of the FTS a distinguished deadlock state  $s_{\dagger} \notin S$  and, for each hidden deadlock state s, adding a new transition (which we call a *deadlock transition*) with s as source,  $s_{\dagger}$  as target, and labelled by a distinguished action  $\dagger \notin \Sigma$  and by a feature expression that negates the disjunction of the feature expressions of all its source state's outgoing transitions.

Note that step (3) needs to be performed only for those hidden deadlock states that have not yet become explicit deadlock states upon the removal of dead transitions in step (1).

Example 5 In Fig. 7(left), we depict an unambiguous FTS  $\mathcal{F}_*$  that was obtained by transforming the ambiguous FTS  $\mathcal{F}$  of Fig. 5. We removed dead transition  $s_2 \xrightarrow{a \mid f_2} s_2$  and false optional transition  $s_1 \xrightarrow{a \mid f_1} s_2$  was turned into must transition  $s_1 \xrightarrow{a \mid T} s_2$ . Note that in this case there was no need to add a deadlock transition from the hidden deadlock state  $s_2$  to a newly added explicit deadlock state, since  $s_2$  has become an explicit deadlock state in the FTS upon removal of the dead transition  $s_2 \xrightarrow{a \mid f_2} s_2$ .

In Fig. 7(right), we depict an unambiguous FTS  $\mathcal{F}'_*$  that was obtained by transforming the ambiguous FTS  $\mathcal{F}'$  of Fig. 6 as follows. We removed the dead transition  $s_2 \xrightarrow{a \mid f_2} s_2$  and we added the deadlock transition  $s_1 \xrightarrow{\dagger \mid \neg f_1 \ } s_{\dagger}$  from the hidden deadlock state  $s_1$  to the newly added explicit deadlock state  $s_1$ . Note that in this case, without adding this deadlock transition, state  $s_1$  would have remained a hidden deadlock state in  $\mathcal{F}'_*$ .

Note that the addition of explicit deadlock states and transitions does not preserve bisimilarity (nor trace equivalence), which means that resolving the ambiguities does not guarantee that the properties of the original FTS are maintained.<sup>2</sup> However, if a modeller decides to resolve ambiguities in an FTS (as signalled by our static analysis) through the introduction of explicit deadlock states and transitions, then even though the resulting FTS is no longer bisimilar to the original one, it has gained in clarity. Furthermore, as anticipated

<sup>&</sup>lt;sup>2</sup>A property can still be verified by minor modifications of the formula (e.g., by expressing the v-ACTLive formula  $EF [\neg a] \top$  as  $EF [\neg a \land \neg \dagger] \top$  or the LTL formula  $\bigcirc \top$  as  $\bigcirc \neg \dagger$ ).

10 Page 12 of 43 Empir Software Eng (2022) 27:10

earlier, a kind of family-based verification on the improved FTS becomes available to the modeller, according to the strategy outlined in Fig. 4.

As said before, an ambiguous FTS may be due to a mistake of the modeller in defining the feature model, in particular in the case of large feature models with many cross-tree constraints. Here we provide a small example, leaving more meaningful examples to Section 6.

Example 6 Consider again the FTS  $\mathcal{F}$  depicted in Fig. 5(left), but now with feature model FM =  $f_1 \rightarrow f_2$ , i.e. the presence of feature  $f_1$  requires that of  $f_2$ . In this case, the LTS  $\mathcal{F}|_{\lambda_1}$  has two further a-transitions, viz. loops in states  $s_0$  and  $s_2$ , meaning that  $\mathcal{F}$  no longer exhibits neither dead transitions nor hidden deadlock states—only the false optional transition  $s_1 \stackrel{a|f_1}{\longrightarrow} s_2$  remains (cf. Examples 3 and 4).

## 5 Detecting ambiguities

In this section, we present an algorithm to detect behavioural ambiguity. It relies on expressing the conditions of being a hidden deadlock state, a dead transition, or a false optional transition in an FTS as propositional formulas (in which the names of the FTS's features, states and transitions are used as propositional variables), thus reducing FTS ambiguity detection to solving a set of SAT problems (Cook 1971) (i.e., to decide whether a given propositional formula is satisfiable). While SAT solving is well known to be NP-complete, SAT solvers are widely used for all kinds of static analysis on feature models with a surprising effectiveness even for models with hundreds of thousands of clauses and tens of thousands of variables (Mendonca et al. 2009; Liang et al. 2015).

To this aim, our implementation exploits an automatic SAT solver. SAT solving is an active field of research (Heule et al. 2021; Bjørner et al. 2015; Hutter et al. 2017; Audemard et al. 2016) and tools exist that compute, more or less efficiently, a solution for an input formula, or fail if the formula is not satisfiable. Hence, by feeding the formula encoding an ambiguity question to a SAT solver, we can obtain an answer to it. In our implementation, we use the Z3 SMT solver (de Moura and Bjørner 2008) (that includes a SAT solver) developed by Microsoft Research and freely available under the MIT license. The python code of our implementation is publicly available (ter Beek et al. 2019c); it accepts FTSs in the format .dot as input and all example models used in the remainder of this paper are provided.

#### 5.1 FTS representation

Our algorithm assumes that the considered FTS is represented by the global data structure fts that includes four fields:

- states stores the set of all states in the FTS;

- 2. transitions stores the set of all transitions in the FTS;

- 3. initial stores the initial state of the FTS;

- 4. fm stores the formula FM (introduced before Example 2 in Section 3), which is a formula in  $\mathbb{B}(F)$  that represents the feature model of the FTS.

Each state is represented by a data structure that includes three fields:

- 1. in\_trs stores the set of incoming transitions of this state;

- out\_trs stores the set of outgoing transitions of this state;

Empir Software Eng (2022) 27:10 Page 13 of 43 10

3. hdead is a Boolean flag used to record whether this state is a hidden deadlock.

Each transition is represented by a data structure that includes four fields:

- 1. bx stores the feature expression labelling the transition, i.e., a propositional formula in  $\mathbb{B}(F)$ ;

- 2. source stores the source state of the transition;

- 3. dead is a Boolean flag used to record whether this transitions is dead;

- 4. false\_opt is a Boolean flag used to record whether this transitions is false optional.

The Boolean flags in each state (field hdead) and transition (fields dead and false\_opt are used to record the results of the analysis (i.e., the output of the algorithm); their initial values are immaterial.

## 5.2 Propositional formulas expressing the conditions to be checked

Let  $\mathcal{F} = (S, \Sigma, s_0, \delta, F, \Lambda)$  be an FTS. Let T be the set of the names of the transitions of the FTS. In this section, we introduce propositional formulas on  $\mathbb{B}(F \cup S \cup T)$  that express the conditions of being a hidden deadlock state, a dead transition, or a false optional transition in the FTS.

Recall that an interpretation for a propositional formula in  $\mathbb{B}(F \cup S \cup T)$  is a function  $\mathcal{I}: (F \cup S \cup T) \longrightarrow \{\top, \bot\}$ . We say that a state or transition is *selected* in an interpretation to mean that the associated propositional variable gets value  $\top$  and, on the other hand, we say it is *deselected* in an interpretation to mean that the associated propositional variable gets value  $\bot$ .

**Notation 1** For the sake of simplicity, we abuse the notation of data structures for states and transitions (cf. Section 5.1). We use fts.states as an alternative name for S, and use fts.transitions as an alternative name for S. We use fts.initial to refer to the initial state S0, use S1 of S2, and use S3 to refer to the corresponding state (an element of S3), and use S3 to fts.transitions, S4 of S5. S5 and S6 of S7.

Let inner\_states denote the set fts.states\{fts.initial}. An *initial path* is a path that starts from the initial state.

We first introduce some propositional formulas that, together with the formula fts.fm, allow us to formalise the conditions that grasp the initial paths in the FTS's products.

- $\phi_{\text{initial}}$  is the formula fts.initial (i.e., the name of the initial state). This formula is valid in an interpretation  $\mathcal{I}$  iff  $\mathcal{I}$  selects the initial state.

- $\phi_{\text{inner}}$  is the formula  $\bigwedge_{s \in \text{inner\_states}}(s \Rightarrow \text{atLeastOneTransition-Of}(s.\text{in\_trs}))$ , where atLeastOneTransitionOf(X) is a placeholder for  $\bigvee_{t \in X} (t.\text{bx} \land t \land t.\text{source})$ . This formula is valid in an interpretation  $\mathcal{I}$  iff  $\mathcal{I}$  selects only states that are reachable via selected transitions, with valid (in  $\mathcal{I}$ ) feature expressions, that are outgoing from selected states.

- $\phi_{\text{single}}$  is the formula  $\bigwedge_{s \in \text{fts.states}} \text{atMostOneOf}(s.\text{out\_trs})$ , where atMostOneOf(X) is a placeholder for  $\bigwedge_{t \in X} t \Rightarrow (\bigwedge_{t' \in X \setminus \{t\}} \neg t')$ . This formula is valid in an interpretation  $\mathcal{I}$  iff  $\mathcal{I}$  selects at most one outgoing transition, for each state (selected or not).

- end(s) is the formula  $s \land (\bigwedge_{t \in s.out\_trs} \neg t)$ . This formula is valid in an interpretation  $\mathcal{I}$  iff  $\mathcal{I}$  selects the state s and deselects all outgoing transitions from that state.

10 Page 14 of 43 Empir Software Eng (2022) 27:10

Next, we focus our attention on the conjunction of the above formulas.

- is\_useful\_state(s) is the formula fts.fm  $\land \phi_{initial} \land \phi_{inner} \land \phi_{single} \land end(s)$ . This formula is satisfiable (i.e., valid in some interpretation  $\mathcal{I}$ ) iff in at least one LTS product there is a simple path (i.e., a path with no repeated states) that starts from the initial state and ends in s.

## Example 7 Consider the FTS on the right.

It has no features and just one product configuration (represented by the mapping from the empty set to  $\mathbb{B}$ ) which yields the LTS consisting of the initial state  $s_0$ . Therefore, fts.fm =  $\top$ . States s and  $s_1$  are not useful (since they are not reachable from  $s_0$ ) and, accordingly, the formulas is\_useful\_state(s) and is\_useful\_state(s) are not satisfiable. To see this, let t be the transition from  $s_1$  to s and let  $t_1$  be the transition from  $s_1$  to  $s_1$ .

- To satisfy is\_useful\_state(s) requires to assign  $\top$  to s (because end(s) must be satisfied), which in turn requires to assign  $\top$  to both t and  $s_1$  (because  $\phi_{inner}$  must be satisfied), which in turn requires to assign  $\bot$  to  $t_1$  (because  $\phi_{single}$  must be satisfied, viz. only t can exit  $s_1$ ), which in turn implies that  $\phi_{inner}$  cannot be satisfied (because at least one transition has to enter  $s_1$ ) and therefore is\_useful\_state(s) cannot be satisfied.

- To satisfy is\_useful\_state( $s_1$ ) requires to assign  $\top$  to  $s_1$  and  $\bot$  to  $t_1$  (because end( $s_1$ ) must be satisfied), which in turn implies that  $\phi_{inner}$  (and therefore is\_useful\_state( $s_1$ )) cannot be satisfied.

We can straightforwardly define the formulas for checking the behavioural ambiguities by exploiting the formula is\_useful\_state(s).

- is\_not\_dead\_transition(t) is the formula is\_useful\_state (t.source) ∧

t.bx. This formula is satisfiable iff the transition t is not dead (cf. Definition 5).

- may\_be\_opt\_transition(t) is the formula is\_useful\_state (t.source) ∧

¬t.bx. This formula is satisfiable iff the LTS transition corresponding to transition t (of the FTS) is not present in at least one of the FTS's products in which its source state is present—thus if t is not dead, then t is not false optional (cf. Definition 6).

Example 8 Consider the FTS  $\mathcal{F}$  of Example 3. Let  $t_0$ ,  $t_1$ ,  $t_2$ , and  $t_3$  be the transitions  $s_0 \xrightarrow{a \mid f_2} s_0$ ,  $s_0 \xrightarrow{a \mid f_1} s_1$ ,  $s_1 \xrightarrow{a \mid f_1} s_2$ , and  $s_2 \xrightarrow{a \mid f_2} s_2$ , respectively.

We have that the formula is\_not\_dead\_transition( $t_3$ ) is not satisfiable (therefore  $t_3$  is dead) and the formula exists\_deadlock( $s_2$ ) is satisfiable (therefore state  $s_2$  is a hidden deadlock).

Moreover, the formula is\_not\_dead\_transition( $t_2$ ) is satisfiable (therefore  $t_2$  is not dead) and the formula may\_be\_opt\_transition( $t_2$ ) is satisfiable (therefore  $t_2$  is false optional).

<sup>&</sup>lt;sup>3</sup>Note that there could be interpretations that fulfill is\_useful\_state(s) and include also non-initial paths, but in any case s must still be reachable by an initial path that is within the interpretation.

Empir Software Eng (2022) 27:10 Page 15 of 43 10

Consider the FTS  $\mathcal{F}'$  of Example 4. Let  $t_0$ ,  $t_1$ ,  $t_2$ , and  $t_3$  be the transitions  $s_0 \xrightarrow{a \mid f_2} s_0$ ,  $s_0 \xrightarrow{a \mid T} s_1$ ,  $s_1 \xrightarrow{a \mid f_1} s_2$ , and  $s_2 \xrightarrow{a \mid f_2} s_2$ , respectively.

We have that the formula is\_not\_dead\_transition( $t_3$ ) is not satisfiable (therefore  $t_3$  is dead). Moreover, both formulas exists\_deadlock( $s_1$ ) and exists\_deadlock( $s_2$ ) are satisfiable (therefore both  $s_1$  and  $s_2$  are hidden deadlocks).

We denote by  $\lambda_{\mathcal{I}}$  the restriction of the interpretation  $\mathcal{I}$  to features.

The following lemma formally states the meaning of the five components of the formula  $is\_useful\_state(s)$ .

**Lemma 1** Let fts be the global data structure that represents the FTS  $\mathcal{F} = (S, \Sigma, s_0, \delta, F, \Lambda)$  and let  $\mathcal{I}$  be an interpretation. Then

- 1.  $\mathcal{I} \models fts.fmiff \lambda_{\mathcal{I}} \in \Lambda$ .

- 2.  $\mathcal{I} \models \phi_{initial} iff \mathcal{I}(fts.initial) = \top$ .

- 3.  $\mathcal{I} \models \phi_{\text{inner}}$  iff, for all  $s \in \text{inner\_states}$ , if  $\mathcal{I}(s) = \top$  then there is at least a transition  $t \in s.\text{in\_trs}$  such that:  $\mathcal{I} \models t.\text{bx}$ ,  $\mathcal{I}(t) = \top$ , and  $\mathcal{I}(t.\text{source}) = \top$ .

- 4.  $\mathcal{I} \models \phi_{single}$  iff, for all  $s \in inner\_states$ , there is at most one transition  $t \in s.out\_trs$  such that  $\mathcal{I}(t) = \top$ .

- 5.  $\mathcal{I} \models end(s) \text{ iff, } \mathcal{I}(s) = \top \text{ and } \mathcal{I}(t) = \bot, \text{ for all } t \in s.out\_trs, \text{ where } s \in fts.states.$

Proof Straightforward.

The next lemma formally states the meaning of the formula is\_useful\_state(s).

**Lemma 2** Let fts be the global data structure that represents the FTS  $\mathcal{F} = (S, \Sigma, s_0, \delta, F, \Lambda)$  and let s' be a state of  $\mathcal{F}$ .

Then the formula  $is\_useful\_state(s')$  is satisfiable iff there are an interpretation  $\mathcal{I}$  and an initial path P of  $\mathcal{F}$  ending in s' such that  $\lambda_{\mathcal{I}} \in \Lambda$  and

- 1.  $\mathcal{I}(s) = \top$ , for each state s visited by P, and

- 2.  $\mathcal{I}(t) = \top$  and  $\lambda_{\mathcal{I}} \models t.bx$ , for each transition t visited by P.

*Proof* We consider first the direction from right to left. Let  $\mathcal{I}$  be an interpretation and P an initial path of  $\mathcal{F}$  ending in s' such that  $\lambda_{\mathcal{I}} \in \Lambda$  and conditions (1) and (2) hold. Consider the interpretation  $\mathcal{I}_0$  that maps to  $\bot$  all the states and transitions that are not in P and behaves as  $\mathcal{I}$  on all other arguments. Then it is immediate to check that  $\mathcal{I}_0 \models \mathtt{is\_useful\_state}(s')$  holds (i.e.,  $\mathtt{is\_useful\_state}(s')$  is satisfiable).

Consider now the other direction. Let  $\mathcal{I}'$  be an interpretation satisfying is\_useful\_state(s'), i.e., such that  $\mathcal{I}' \models \text{fts.fm}$ ,  $\mathcal{I}' \models \phi_{\text{initial}}$ ,  $\mathcal{I}' \models \$\phi_{\text{inner}}$ ,  $\mathcal{I}' \models \phi_{\text{single}}$ , and  $\mathcal{I}' \models \text{end}(s')$  hold.

Immediately,  $\lambda_{\mathcal{I}'} \in \Lambda$  follows from  $\mathcal{I}' \models \mathsf{fts.fm}$ , while  $\mathcal{I}'(\mathsf{fts.initial}) = \top$  and  $\mathcal{I}'(s') = \top$  follow from  $\mathcal{I}' \models \phi_{\mathsf{initial}}$  and  $\mathcal{I}' \models \mathsf{end}(s')$ , respectively.

Then the proof follows by induction on the number n of states selected by  $\mathcal{I}'$  (note that n must be at least one, since fts.initial is always selected).

- If n = 1, then we are selecting only one state, i.e., s' and the initial state coincide. Hence, the initial path is just s' and the proof that conditions (1) and (2) hold is immediate.

10 Page 16 of 43 Empir Software Eng (2022) 27:10

Let n > 1. If s' is the initial state, then the proof is immediate (as for the case n = 1). Thus, let s' be different from the initial state. We know that s' is selected in whatever interpretation satisfying is\_useful\_state(s'). By Lemma 1(3), we know that there are  $m \ge 1$  transitions  $\{t_1, \ldots, t_m\} \in s.in\_trs$  such that  $\mathcal{I}' \models t_i.bx$ ,  $\mathcal{I}'(t_i) = \top$ , and  $\mathcal{I}'(t_i.source) = \top$ . Moreover, we know that  $s'.out\_trs = \emptyset$  by Lemma 1(5).

Let  $\mathcal{I}_0$  be the interpretation that maps  $\{s', t_1, \ldots, t_m\}$  in  $\bot$  and behaves as  $\mathcal{I}'$  on all other arguments. For all transitions  $t_i$ , we have that  $\mathcal{I}_0 \models \operatorname{end}(t_i.\operatorname{source})$  holds, because by Lemma 1(3) there is at most a selected transition outgoing from  $t_i.\operatorname{source}$  in  $\mathcal{I}'$  and we deselected it. Moreover,  $\mathcal{I}_0 \models \operatorname{fts.fm}, \mathcal{I}_0 \models \phi_{\operatorname{initial}}, \mathcal{I}_0 \models \phi_{\operatorname{inner}},$  and  $\mathcal{I}_0 \models \phi_{\operatorname{single}}$  hold. Therefore  $\mathcal{I}_0 \models \operatorname{is\_useful\_state}(t_i.\operatorname{source})$  holds.

By induction we have that there are a configuration  $\lambda_{\mathcal{I}_0} \in \Lambda$  and a selected initial path  $\mathsf{P}_0$  of  $\mathcal{F}|_{\lambda_{\mathcal{I}_0}}$  that reaches  $t_1$ . source and (together with  $\mathcal{I}_0$ ) satisfies conditions (1) and (2). Clearly,  $\lambda_{\mathcal{I}_0} = \lambda_{\mathcal{I}'}$  (by construction of  $\mathcal{I}_0$ ). Extending  $\mathsf{P}_0$  with the transition  $t_1$  and the state s', we obtain an initial path  $\mathsf{P}'$  that reaches s' and (together with  $\mathcal{I}'$ ) satisfies conditions (1) and (2).

Finally, the following theorem formally states the correctness of the formulas  $exists\_deadlock(s)$ ,  $is\_not\_dead\_transition(t)$ , and  $may\_be\_opt\_transition(t)$ .

**Theorem 1** (correctness of the formulas for checking the behavioural ambiguities) Let fts be the global data structure representing the FTS  $\mathcal{F} = (S, \Sigma, s_0, \delta, F, \Lambda)$  and let s be a state of  $\mathcal{F}$ . Then

- 1. The formula exists\_deadlock(s) is satisfiable iff there is a configuration  $\lambda \in \Lambda$  such that the state s is a deadlock in  $\mathcal{F}|_{\lambda}$ .

- 2. The formula is\_not\_dead\_transition(t) is satisfiable iff there is a configuration  $\lambda \in \Lambda$  such that the LTS transition corresponding to transition t is reachable in  $\mathcal{F}|_{\lambda}$ .

- 3. The formula may\_be\_opt\_transition(t) is satisfiable iff there is a configuration  $\lambda \in \Lambda$  such that the state t.source is reachable in  $\mathcal{F}|_{\lambda}$  and the LTS transition corresponding to transition t is not reachable in  $\mathcal{F}|_{\lambda}$ .

*Proof* Straightforward from Lemma 2.

## 5.3 Algorithms

The algorithm in Listing 1 below uses the function check to verify whether a propositional formula  $\phi$  is satisfiable, namely to verify the existence of an interpretation (an assignment of truth values to propositions in  $\mathbb{B}(F \cup S \cup T)$ ) that makes the formula valid. This is the core functionality of all SAT solvers.

**Theorem 2** (correctness of the ambiguities discovery algorithm) *Let fts be a data structure representing an FTS. The execution of the algorithm in Listing 1 terminates and at the end of the execution the following holds.*

- 1. For each state s,

- if s is a hidden deadlock, then s.hdead = True; otherwise s.hdead = False.

- 2. For each transition t,

Empir Software Eng (2022) 27:10 Page 17 of 43 10

```

1

# fts contains the input FTS (according to Section 5.1)

2

3

for s in fts.states:

4

if(s.out\_trs = \emptyset):

5

s.hdead \leftarrow False

7

s.hdead \leftarrow check(exist deadlock(s))

8

9

# for all states s, it holds that:

10

# (s.hdead ≡ ''s is a hidden deadlock'')

11

12

for s in fts.states:

13

for t in s.in_trs:

14

t.dead ←not check(is_not_dead_transition(t))

15

if (t.dead or t.bx = T):

16

t.false\_opt \leftarrow False

17

else:

18

t.false\_opt \leftarrow not check(may\_be\_opt\_transition(t))

19

20

# for all transitions t, it holds that:

# (t.dead \equiv ''t is dead'') and (t.false\_opt \equiv

2.1

"'t is false optional'')

```

Listing 1 Ambiguities discovery algorithm

- (a) if t is dead, then t.dead = True; otherwise t.dead = False;

- (b) if t is false optional, then t.false\_opt = True; otherwise t.false\_opt = False.

*Proof* Correctness of the formulas  $exists\_deadlock(s)$ ,  $is\_not\_dead\_transition(t)$ , and may\_be\_opt\_transition(t) is stated by Theorem 1.

The algorithm first detects all the hidden deadlocks (lines 3–7, where the test in line 4 detects the states that are deadlocks in the FTS), thus establishing the invariant in lines 9–10.

Then it detects all the dead transitions and all the false optional transitions (lines 12–18, where the test in line 15 detects the dead transitions that cannot be false optional because they are dead or labelled with  $\top$ ), thus establishing the invariant in lines 20–21 while keeping the invariant in lines 9–10 (since the Boolean flags hdead of the states are not modified).

The termination of the algorithm is straightforward since the number of states and transitions of the FTS is finite.  $\Box$

It is worth observing that, whenever one is only interested in detecting the hidden dead-locks, it is enough to run only the first part (lines 1–10) of the algorithm in Listing 1: this part represents a specialised algorithm that only detects hidden deadlocks.

Remark 1 (The FTS ambiguity detection problem is NP-complete) For every propositional formula  $\phi$  with variables in F, the FTS

$$(\{s_0, s\}, \{a\}, s_0, \{s_0 \xrightarrow{a \mid \phi} s\}, F, 2^F)$$

is such that its (unique) transition is: (i) dead if and only if  $\phi$  is not satisfiable (i.e.  $\neg \phi$  is valid); and (ii) false optional if and only if  $\neg \phi$  is not satisfiable (i.e.  $\phi$  is valid). Moreover, state  $s_0$  is a hidden deadlock if and only if  $\phi$  is not satisfiable. Thus, the FTS ambiguity detection problem is NP-hard. Moreover, the algorithm in Listing 1 can be transformed into an algorithm that, given the data structure fts (cf. Section 5.1) representing an FTS  $\mathcal{F}$  with

10 Page 18 of 43 Empir Software Eng (2022) 27:10

n states and m transitions, reduces (in polynomial time in the size of fts) the ambiguity detection problem for  $\mathcal{F}$  to  $n+2\times m$  SAT problems (each problem consisting of a formula whose size is linear in the size of fts), as follows:

- extend the data structure introduced in Section 5.1 by adding a field hdead\_formula to each state and by adding a field dead\_formula and a field false\_optional\_formula to each transition;

- replace line 7 by s.hdead\_formula := exist\_deadlock(s);

- replace line 14 by t.dead\_formula := is\_not\_dead\_transition(s); and

- replace lines 15–18 by t.false\_opt\_formula := may\_be\_opt\_transition(s).

Solving the SAT problems stored in the fields hdead\_formula, dead\_formula, and false\_optional\_formula provides a solution to the ambiguity detection problem for the given FTS, therefore we conclude that the FTS ambiguity detection problem is NP-complete.

## 6 Benchmark examples

In this section, we apply the new algorithm to a number of exemplary FTSs from the literature. The python code of the implementation and all FTS models allowing the verification of the examples presented in this section are publicly available (ter Beek et al. 2019c). We first discuss the experiments (in Section 6.1) and then the corresponding performance results (in Section 6.2).

## 6.1 Experiments

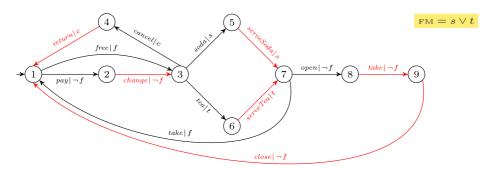

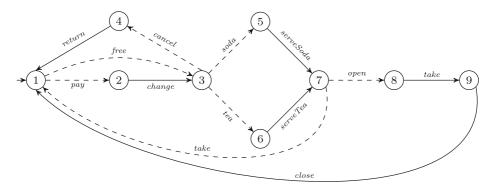

**Vending Machine** In Fig. 8, we depict the FTS modelling the behaviour of a configurable vending machine from Classen (2011), an FTS benchmark which was used in ter Beek et al. (2019a) and in many other publications (Classen et al. 2010, 2013; Devroey et al. 2014b, 2016b; ter Beek et al. 2015a, 2015b, 2019b; Dimovski et al. 2017; Dimovski and Wąsowski 2017; Castro et al. 2018; Dimovski 2018, 2020; Dubslaff 2019). It serves a beverage (soda or tea) either for free or upon payment, in which case a compartment is opened for the customer to take the beverage after which it closes again. Its feature model is represented by the formula  $s \lor t$  over the 4 features  $\{f, c, s, t\}$ , thus resulting in 12 product configurations (viz.  $2^4 - 4$ , excluding the product configurations  $\emptyset$ ,  $\{f\}$ ,  $\{c\}$ , and  $\{f, c\}$  that lack both features s for soda and t for tea). The FTS of the vending machine contains only 9 states and 13 transitions.

Listing 2 reports the result of applying our static analysis algorithm to this FTS. The FTS contains no dead transitions and no hidden deadlocks, but it does contain the 6 false optional transitions  $(2, change, \neg f, 3)$ , (4, return, c, 1), (5, serveSoda, s, 7), (6, serveTea, t, 7),  $(8, take, \neg f, 9)$ , and  $(9, close, \neg f, 1)$ . Thus, the FTS is ambiguous, but it would suffice to turn its false optional transitions into must transitions to make the FTS unambiguous.

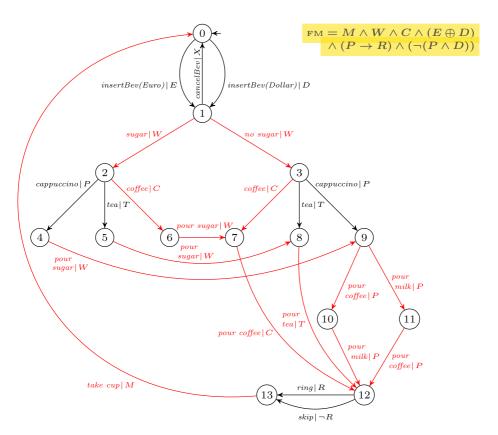

**Coffee Machine** In Fig. 9, we depict the FTS modelling the behaviour of a configurable coffee machine family from Belder et al. (2015). Originally introduced in Fantechi and Gnesi (2008), this is another SPL benchmark which was already used in ter Beek et al. (2019a) and in a number of other publications (Asirelli et al. 2010, 2011;

Empir Software Eng (2022) 27:10 Page 19 of 43 10

Fig. 8 FTS of the vending machine from Classen (2011)

ter Beek et al. 2012, 2013, 2015c, 2016a, 2016b; ter Beek and de Vink 2014a, 2014b; Beohar et al. 2016, 2018). The coffee machine serves a (possibly sugared) beverage (coffee, tea, or cappuccino) upon the insertion of a coin (euro or dollar), after which the customer takes her/his beverage (possibly following a ringtone). Its feature model is represented by the formula  $FM_C = M \wedge W \wedge C \wedge (E \oplus D) \wedge (P \rightarrow R) \wedge (\neg (P \wedge D))$  over the features  $F_C = \{M, W, C, E, D, P, R, T, X\}$ , resulting in 12 product configurations which accept either euros or dollars and offer coffee (with sugar) and possibly tea and cappuccino (upon a ringtone and only for euros). The FTS of the coffee machine contains 14 states and 23 transitions.

Listing 3 reports the result of applying our static analysis algorithm to this FTS. The FTS contains no dead transitions and no hidden deadlocks, but it contains 14 false optional transitions such as (1, sugar, W, 2), (1, no sugar, W, 3), (2, coffee, C, 6), (8, pour tea, T, 12), and (13, take cup, M, 0). Thus, the FTS is ambiguous, but it would suffice to turn its false optional transitions into must transitions to make the FTS unambiguous.

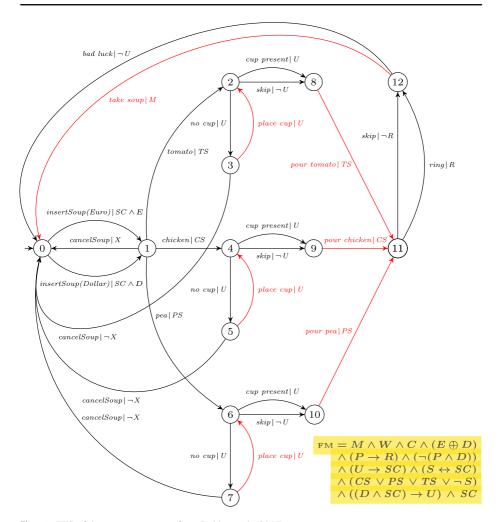

**Coffee/Soup Machine** In Belder et al. (2015), this family of coffee machines was extended with an optional soup component running in parallel with the beverage component. The FTS modelling the behaviour of this soup component is depicted in Fig. 10.<sup>5</sup> The resulting family of vending machines is such that each product allows the insertion of either euros or dollars (returned upon a cancel) in one of its components. The customer chooses a beverage or, if available, a type of soup (at least one among chicken, tomato, pea), which requires to place a cup. A cup detector is optional (mandatory for dollars). Whenever present, soup is only poured if a cup was placed. Placing a cup may need to be repeated if not detected. A choice for soup may be cancelled until a cup is detected. Optionally, a ringtone may ring upon delivery (mandatory for cappuccino, as before), after which the customer takes her/his cup (with a drink or soup) and can again insert a coin in one of the components. The feature model of the soup component is represented by the formula  $FM_C \wedge FM_S \wedge SC$ , where  $FM_S = (U \rightarrow SC) \wedge (S \leftrightarrow SC) \wedge (CS \vee PS \vee TS \vee \neg S) \wedge ((D \wedge SC) \rightarrow U)$ , over the features  $F_C \cup \{SC, U, S, CS, PS, TS\}$ . The FTS of the soup component contains 13 states and 28 transitions.

<sup>&</sup>lt;sup>4</sup>The only differences between the FTS used here and the one in ter Beek et al. (2019a) is the additional transition (1, cancelBev, X, 0), which allows to cancel a coin insertion in the presence of an additional optional feature X, next to a renaming of the states and the features.

<sup>&</sup>lt;sup>5</sup>While omitted in the component FTS drawn in Belder et al. (2015), once put in parallel, coin insertion for soup requires the presence of the soup component (e.g.,  $(0, insertSoup(Euro), SC \land E, 1)$ .

10 Page 20 of 43 Empir Software Eng (2022) 27:10

```

VENDING MACHINE: live

LIVE STATES = [1,2,3,4,5,6,7,8,9]

DEAD TRANSITIONS = []

FALSE OPTIONAL TRANSITIONS = [(2,3,change),(4,1,return),(5,7,serveSoda),(6,7,serveTea),(8,9,take),(9,1,close)]

HIDDEN DEADLOCK STATES = []

```

**Listing 2** Result of the static analysis on the FTS of Fig. 8

Listing 4 reports the result of applying our static analysis algorithm to this FTS. The FTS contains no hidden deadlocks and no dead transitions, but it contains the 7 false optional transitions  $(3, place\ cup,\ U,\ 2),\ (5, place\ cup,\ U,\ 4),\ (7, place\ cup,\ U,\ 6),\ (8, pour\ tomato,\ TS,\ 11),\ (9, pour\ chicken,\ CS,\ 11),\ (10, pour\ pea,\ PS,\ 11),\ and\ (12, take\ soup,\ M,\ 0).$  Thus, the FTS is ambiguous, but it would suffice to turn its false optional transitions into must transitions to make the FTS unambiguous.

The feature model of the composite FTS that results from running the (optional) soup component depicted in Fig. 10 in parallel with the beverage component of the FTS of the coffee machine depicted in Fig. 9 is represented by the formula  $FM_C \wedge FM_S$  over the features

Fig. 9 FTS of the coffee machine from Belder et al. (2015)

Empir Software Eng (2022) 27:10 Page 21 of 43 10

```

COFFEE MACHINE: live

LIVE STATES = [0,1,2,3,4,5,6,7,8,9,10,11,12,13]

DEAD TRANSITIONS = []

FALSE OPTIONAL TRANSITIONS = [(1,2,sugar),(1,3,no_sugar),(2,6,coffee),(3,7,coffee),(6,7,pour_sugar),(5,8,pour_sugar),(4,9,pour_sugar),(9,11,pour_milk),(9,10,pour_coffee),(8,12,pour_tea),(7,12,pour_coffee),(11,12,pour_coffee),(10,12,pour_milk),(13,0,take_cup)]

HIDDEN DEADLOCK STATES = []

```

Listing 3 Result of the static analysis on the FTS of Fig. 9

$F_c \cup \{SC, U, S, CS, PS, TS\}$ , giving rise to 244 product configurations.<sup>6</sup> The composite FTS contains 182 states and 691 transitions.

Listing 5 reports the result of applying our static analysis algorithm to this composite FTS. The composite FTS contains no hidden deadlocks, 284 false optional transitions and 8 dead transitions. The false optional transitions are obviously due to the relatively large amount of false optional transitions in the two component FTSs. The dead transitions can be explained by analysing the execution traces. Consider, for instance, the dead transition (12, *insertSoupDollar*,  $SC \land D$ , 29). Its source state can be reached upon inserting a coin, followed by choosing sugar and ordering cappuccino, which we recall to require feature P. If the inserted coin was a euro, requiring feature E, then the transition cannot be executed since features E and D exclude each other, while if the inserted coin was a dollar, requiring feature D, then the transition cannot be executed since P and D exclude each other. Since any product has either D or E, indeed in all product LTSs this transition is not reachable. A similar reasoning applies to the *skip* transitions, which require a feature R that cannot be part of product LTSs in which their sources states are reachable. Hence, the FTS is ambiguous, but it would suffice to remove its dead transitions and turn its false optional transitions into must transitions to make the FTS unambiguous.

Since neither the beverage component nor the soup component has any dead transitions, this shows that the parallel composition of FTSs (with some features in common) without dead transitions may result in a composite FTS with dead transitions. Furthermore, the size of the composite FTS is such that analysis by hand is infeasible. In the remainder of this section, we consider even larger examples to illustrate the scalability of our approach.

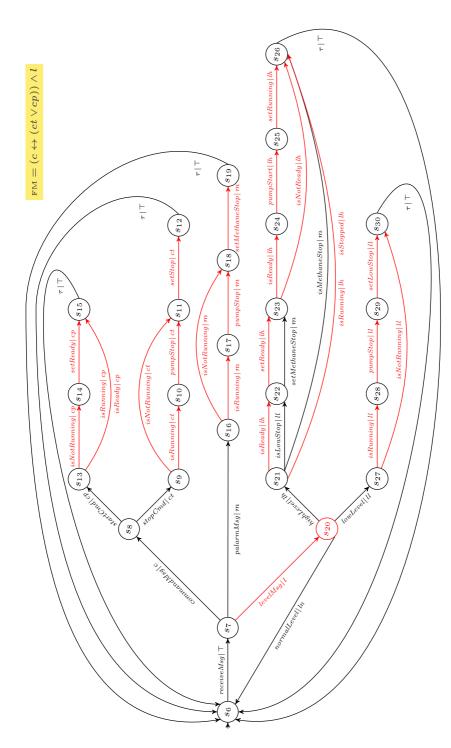

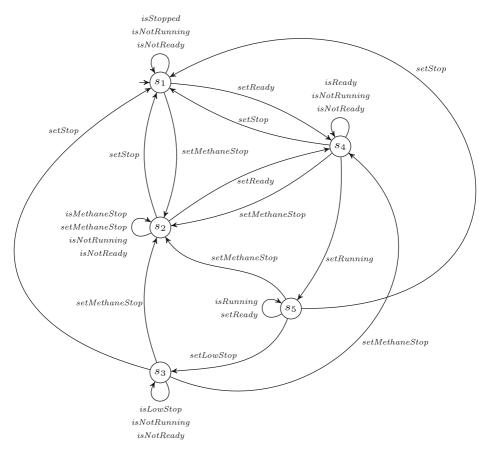

**Mine Pump** In Fig. 11, we depict the FTS modelling the behaviour of the *system* FTS modelling the logic of a configurable controller of the mine pump model from Classen (2010, 2011), a standard SPL benchmark for FTSs which was used in ter Beek et al. (2019a) and in many other publications (Classen et al. 2010, 2012, 2013; Cordy et al. 2012, 2013b; Dimovski et al. 2015, 2017; Devroey et al. 2016b; ter Beek et al. 2017, 2020b; Dimovski and Wąsowski 2017). The controller of this mine pump model is the parallel composition of the *system* FTS with the *state* FTS, depicted in Fig. 12. The mine pump has to keep a mine safe from flooding by pumping water from a shaft while avoiding a methane explosion.

Therefore, the controller interacts with an environment: it operates a water pump based on water and methane level sensors, modelled by three further FTSs. The parallel composition of these five FTSs constitutes the complete mine pump model. We depict the FTS of the

<sup>&</sup>lt;sup>6</sup>In Belder et al. (2015), only 118 of these configurations are valid due to additional quantitative constraints on feature attributes omitted here (e.g. cost of features). We also omitted some mandatory features that do not occur in the FTSs and are thus irrelevant for our purposes.

10 Page 22 of 43 Empir Software Eng (2022) 27:10

Fig. 10 FTS of the soup component from Belder et al. (2015)

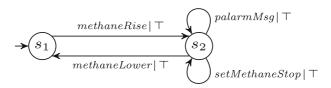

methane level in Fig. 13 and refer to Classen (2010, 2011) for the remaining FTSs. The feature model of the mine pump model can be represented by the formula  $\phi = (c \leftrightarrow (ct \lor cp)) \land l$  over the feature set  $F = \{c, ct, cp, m, l, ll, ln, lh\}$ , thus resulting in 64 products (viz.  $2^6$ , since  $\phi$  is equivalent to considering features  $\{ct, cp, m, ll, ln, lh\}$  to be optional). The *system*

```

SOUP COMPONENT: live

LIVE STATES = [0,1,2,3,4,5,6,7,8,9,10,11,12]

DEAD TRANSITIONS = []

FALSE OPTIONAL TRANSITIONS = [(3,2,place_cup),(5,4,place_cup),(7,6,place_cup),(8,11,pour_tomato),(9,11,pour_chicken),(10,11,pour_pea),(12,0,take_soup)]

HIDDEN DEADLOCK STATES = []

```

Listing 4 Result of the static analysis on the FTS of Fig. 10

Empir Software Eng (2022) 27:10 Page 23 of 43 10

```

COFFEE SOUP MACHINE: live

LIVE STATES = [1,2,...,182]

DEAD TRANSITIONS = [(12,29,insertSoupDollar), (16,38,insertSoupDollar),

(36,72,insertSoupDollar), (37,73,insertSoupDollar), (136,165,skip),

(161,177,skip), (175,180,skip), (176,181,skip)]

FALSE OPTIONAL TRANSITIONS = [(2,4,sugar), (2,5,no_sugar),..., (182,64,take_soup)]

HIDDEN DEADLOCK STATES = []

```

**Listing 5** Result of the static analysis on the composite FTS resulting from the parallel composition of the beverage component of the FTS of the coffee machine depicted in Fig. 9 and the soup component depicted in Fig. 10

FTS of the mine pump model contains 25 states and 41 transitions.<sup>7</sup> The controller of the mine pump model, composed of the *system* and *state* FTSs, contains 77 states and 104 transitions. The complete mine pump model, composed of five FTSs, contains 418 states and 1,255 transitions.

Listing 6 reports the result of applying our static analysis algorithm to the *system* FTS. The FTS contains no dead transitions, but 25 false optional transitions, among which  $(s_7, levelMsg, l, s_{20})$ , and one hidden deadlock state, viz.  $s_{20}$ . Indeed, state  $s_{20}$  is reachable in all products upon the execution of two must transitions (the second one being the false optional transition  $(s_7, levelMsg, l, s_{20})$ ), while  $s_{20}$  is a deadlock in all 8 products that lack any of the features from the subset  $\{ll, ln, lh\}$ .

Hence the *system* FTS is ambiguous, but it would suffice to turn its false optional transitions into must transitions and to add an explicit deadlock state  $s_{\dagger}$  and a transition  $(s_{20}, \dagger, \neg ll \land \neg ln \land \neg lh, s_{\dagger})$  to make the *system* FTS unambiguous.

Yet another solution to make the *system* FTS unambiguous would be to slightly change the FTS itself, to make sure that it contains neither a hidden nor an explicit deadlock state. In this case, it would suffice to add one or more transitions to leave state  $s_{20}$  in a meaningful way. This is the solution opted for in Classen et al. (2013), Dimovski et al. (2015), Dimovski et al. (2017), ter Beek et al. (2017), and Dimovski and Wąsowski (2017), which use the specification in fPromela of the complete mine pump model as originally distributed with SNIP (Classen et al. 2012) and its re-engineered successor ProVeLines (Cordy et al. 2013a) (https://bitbucket.org/maxcordy/provelines-cora/) or their translations for mCRL2 (Cranen et al. 2013; Bunte et al. 2019) (http://www.mcrl2.org/) or VMC (ter Beek et al. 2012; ter Beek and Mazzanti 2014) (http://fmt.isti.cnr.it/vmc/). Basically, three transitions are added to the *system* FTS of Fig. 11 from state  $s_{20}$  to the initial state  $s_{6}$  to cover the cases in which features from the subset {ll, ln, lh} are missing, viz. ( $s_{20}$ , highLevel,  $\neg lh$ ,  $s_{6}$ ), ( $s_{20}$ , lowLevel,  $\neg ll$ ,  $s_{6}$ ), and ( $s_{20}$ , normalLevel,  $\neg ln$ ,  $s_{6}$ ).

The false optional transitions and the hidden deadlock state of the *system* FTS are propagated into the controller of the mine pump model, which we recall to be the parallel

<sup>&</sup>lt;sup>7</sup>Transitions with more than one label are abbreviations for one transition for each label.

10 Page 24 of 43 Empir Software Eng (2022) 27:10

**Fig. 11** The *system* FTS of the mine pump model from Classen (2011) (we have labelled transitions that were unlabelled with  $\tau(\top)$

Empir Software Eng (2022) 27:10 Page 25 of 43 10

Fig. 12 The state FTS of the mine pump model from Classen (2011)

composition of the *system* and *state* FTSs. Application of our static analysis algorithm to the FTS of the controller of the mine pump model reports that the FTS contains no dead transitions, 59 false optional transitions, and 4 hidden deadlock states. The situation is different for the complete mine pump model, which we recall to be the parallel composition of five FTSs, viz. the *system* and *state* FTSs and three further FTSs that model a water pump and water and methane level sensors. From the FTS of the methane level, depicted in Fig. 13, we immediately note that the actions *methaneRise* and *methaneLower* are local actions of this FTS that do not synchronise with any of the other four FTSs. Hence, while the solutions suggested above would make the *system* FTS of Fig. 11 unambiguous, it is clear that

Fig. 13 FTS of the methane level environment from Classen (2011)

10 Page 26 of 43 Empir Software Eng (2022) 27:10

```

MINE PUMP: not live

LIVE STATES = [S6,S7,...,S19,S21,S22,...,S30]

DEAD TRANSITIONS = []

FALSE OPTIONAL TRANSITIONS = [(S7,S20,levelMsg),(S9,S10,isRunning),...,

(S29,S30,setLowStop)]

HIDDEN DEADLOCK STATES = [S20]

```

Listing 6 Result of the static analysis on the FTS of Fig. 11

the FTS of the complete mine pump model is deadlock-free, since it can indefinitely execute the sequence of actions *methaneRise* followed by *methaneLower*. This is confirmed by our static analysis algorithm applied to the FTS of the complete mine pump model, which reports that the FTS contains no dead transitions and no hidden deadlock states, but a stunning 308 false optional transitions. The fact that the *system* FTS has hidden deadlock states that are no longer present in the FTS of the complete mine pump model demonstrates the usefulness of analysing component FTSs in isolation.

In general, while the parallel composition of unambiguous FTSs does not introduce false optional transitions, the composite FTS may contain dead transitions or hidden deadlock states. We have seen an example of the introduction of dead transitions in the composite FTS of the coffee and soup component, whose individual FTSs did not exhibit dead transitions.

The application of the static analysis algorithm to individual component FTSs is surely desirable as it results in less ambiguous specifications of the components constituting a composed system, and it possibly allows more efficient model checking of the composed system (more on this in the next section, cf. the part of Fig. 4 that is not red). A further advantage is that our approach becomes applicable also to feature-oriented systems composed by superimposition, since in Dubslaff (2019) it is shown how to transform feature-oriented systems composed by parallel composition into feature-oriented systems composed by superimposition while maintaining behaviour and modularity.